Synthesis and Static Timing Analysis(STA) & Demo with tools

Published 12/2024

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch

Level: All | Genre: eLearning | Language: English | Duration: 9 Lectures ( 16h 44m ) | Size: 6.31 GB

Published 12/2024

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch

Level: All | Genre: eLearning | Language: English | Duration: 9 Lectures ( 16h 44m ) | Size: 6.31 GB

ASIC flow, Synthesis, STA, Genus tool flow, Tempus tool flow, Timing concepts, paths, constraints

What you'll learn

ASIC Flow in brief

Logical Synthesis vs Physical Synthesis

Timing Concepts, definitions

Static Timing Analysis (STA)

Timing paths, Contraints, modes

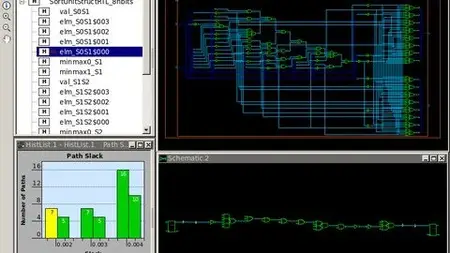

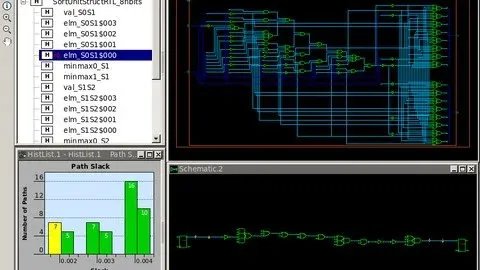

Synthesis example execution with Genus tool

STA example execution with Tempus tool

Requirements

Basics of RTL design using Verilog

Digital Fundamentals

Verilog Language

Description

The course Synthesis and Static Timing Analysis (STA) is intended for all levels of students, who want to gain knowledge in ASIC synthesis and STA. Electronics students, who want to internships, Engineers who want to start career in VLSI field. The course covers the following chapters: 1. ASIC flow in brief2. Logical synthesis - inputs and outputs of synthesis, synthesis constraints, Libraries, Synthesis demo using Cadence Genus tool flow3. Physical Synthesis - Various file formats and descriptions, Physical dimensions of gates4. Timing concepts - Setup time, hold time, slack. violations, timing budgets5. Timing paths - Clock to output, propagation delay, input delay, output delay etc, STA using Cadence Tempus tool flow6. Timing constraints and various modes - MMMC7. Timing Exceptions - False path, multi cycle pathAll the topics are elaborated with detailed examples, illustrated with diagrams, where required. Clear explanation; assignments added at the end of the course for practicing hands on examples. The lecture is given by hands on practitioners from the VLSI industry, who have worked on multiple projects and taped out chipsFor best take away from the course, kindly do hands on using tools (may be available in your institutions/companies). All the best - Happy learning

Who this course is for

Internship - BE/BTech/MTech students and Engineers with ECE/EEE background

Beginners who wants to start VLSI career in ASIC backend activities