Cadence XCELIUM version 23.03.002 | 3.3 Gb

Cadence Design Systems, Inc., the leader in global electronic design innovation, is pleased to announce the availability of XCELIUM Main 23.03.002 (hotfix) is part of the Cadence Verification Suite and supports the company’s Intelligent System Design strategy, enabling pervasive intelligence and faster design closure.

XCELIUM Main Version 23.03.002 - Date: April, 2023

=============================================

CCRID Product Title

–––––––- –––––––––––– –––––––––

JIRA ID COMPONENT SUMMARY

–––––––- –––––––––––– –––––––––

AVSREQ-181401 LP_ISOLATION "-source -sink -no_isolation" does not work for split wire

AVSREQ-185458 LP_ISOLATION Elaboration with LP shows large degradation in elaboration time

AVSREQ-186545 LP_1801 21.03.013 works, 22.09.003 tool crash

AVSREQ-189028 SPECTRE_AMSD xmsim: *E,SYFATAL (****): Illegal port instantiation.

AVSREQ-185965 SIM_SV_VHDL $export_frcrel does not work for VHDL on Xcelium 22.04.a071 and later version

AVSREQ-189447 LP_MSIE MESSAGE: pwr_finalize_iso - Finalize iso for primary snapshot needs [xxx] to be hooked up

AVSREQ-188980 GLS_GENERAL The wires used within tranif0 and tranif1 are throwing "X" which is unexpected.

CCRID Product Title

–––––––- –––––––––––– –––––––––

JIRA ID COMPONENT SUMMARY

–––––––- –––––––––––– –––––––––

AVSREQ-181401 LP_ISOLATION "-source -sink -no_isolation" does not work for split wire

AVSREQ-185458 LP_ISOLATION Elaboration with LP shows large degradation in elaboration time

AVSREQ-186545 LP_1801 21.03.013 works, 22.09.003 tool crash

AVSREQ-189028 SPECTRE_AMSD xmsim: *E,SYFATAL (****): Illegal port instantiation.

AVSREQ-185965 SIM_SV_VHDL $export_frcrel does not work for VHDL on Xcelium 22.04.a071 and later version

AVSREQ-189447 LP_MSIE MESSAGE: pwr_finalize_iso - Finalize iso for primary snapshot needs [xxx] to be hooked up

AVSREQ-188980 GLS_GENERAL The wires used within tranif0 and tranif1 are throwing "X" which is unexpected.

Cadence's Xcelium Logic Simulation provides best-in-class core engine performance for SystemVerilog, VHDL, mixed-signal, low power, and x-propagation. It supports both single-core and multi-core simulation, incremental and parallel build, and save/restart with dynamic test reload. The Xcelium Logic Simulator has been deployed by a majority of top semiconductor companies, and a majority of top companies in the hyperscale, automotive and consumer electronics segments. Using computational software and a proprietary machine learning technology that directly interfaces to the simulation kernel, Xcelium learns iteratively over an entire simulation regression. It analyzes patterns hidden in the verification environment and guides the Xcelium randomization kernel on subsequent regression runs to achieve matching coverage with reduced simulation cycles. Xcelium is part of the Cadence Verification Suite and supports the company’s Intelligent System Design strategy, enabling pervasive intelligence and faster design closure.

Accelerating DFT Simulations with Xcelium Multi-Core

Are long DFT simulations posing a big challenge to meet your tight project schedules? We have a solution to accelerate the long running DFT tests. Watch this video to know how easy it is to set-up Xcelium Multi-Core to get up to 5X acceleration for a variety of DFT use cases ranging from serial and parallel ATPG to MBIST and LBIST

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

Product: Cadence XCELIUM

Version: 23.03.002 (XCELIUMMAIN) hotfix

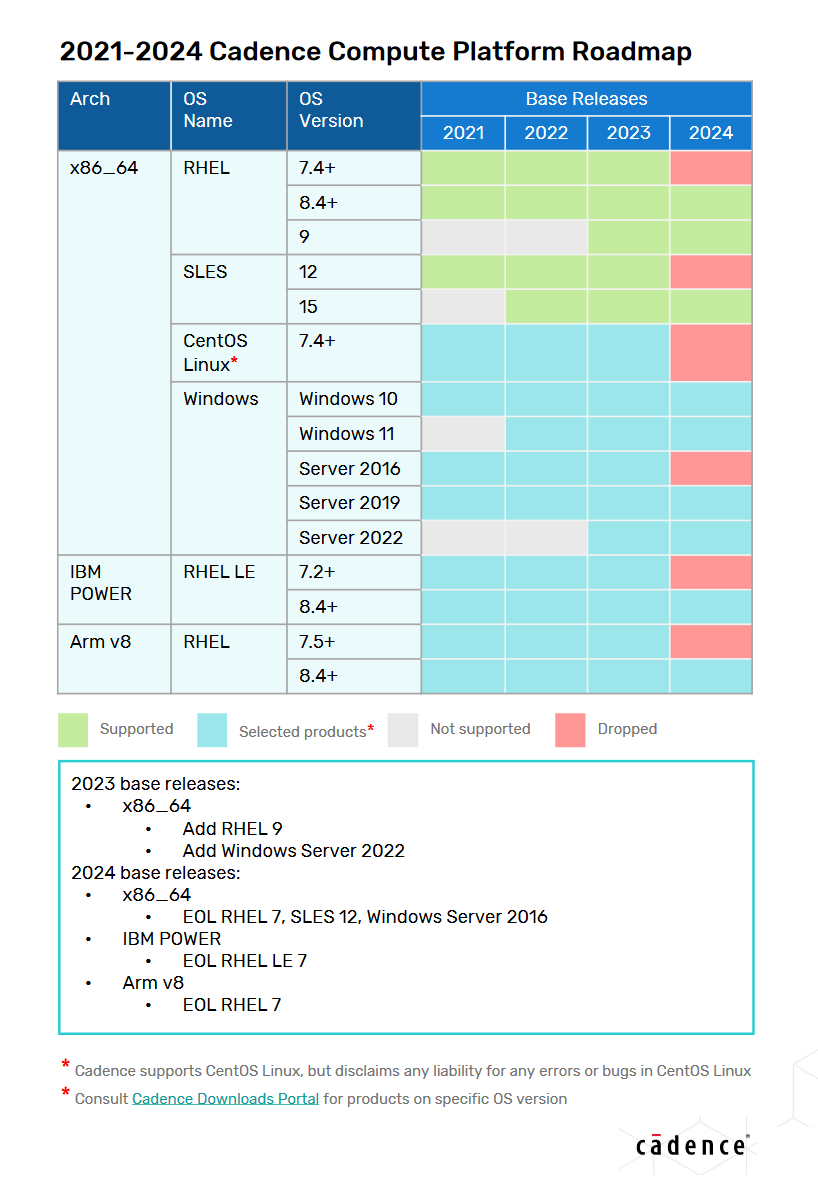

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 3.3 Gb

Cadence XCELIUM version 23.03.001 Base

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please