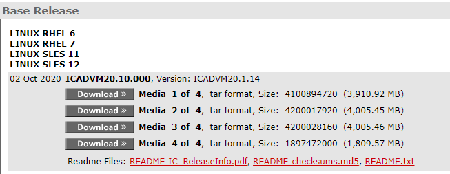

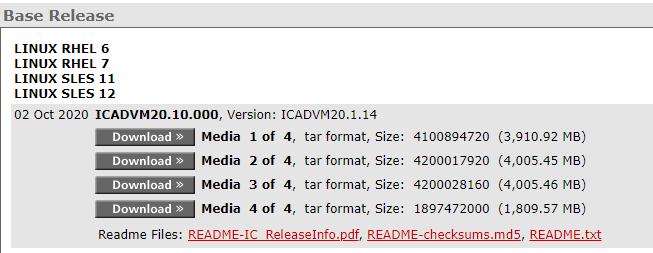

Cadence Virtuoso, Release Version ICADVM20.1 ISR31 | 111.9 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has released Virtuoso ICADVM20.1 ISR31 is a holistic, system-based solution that provides the functionality to drive simulation and LVS-clean layout of ICs and packages from a single schematic.

Cadence Virtuoso, Release Version ICADVM20.1 ISR31 Release Notes

2332454 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2332071 Cannot change the test name in maestro view in ADE Explorer

2327724 The CSV file in which the setup is exported from the Results tab in ADE Assembler is not saved at the desired location

2327005 Wrong column header exporting CSV file from detail transpose

2326741 Virtuoso exits unexpectedly due to an internal application error

2326292 Running 'runsv' reports 'runams' instead of 'runsv'

2326286 Virtuoso exits unexpectedly when editing a figGroup

2325395 Create Via command violates shape boundary for polygonal shapes

2325056 Virtuoso exits unexpectedly when saving constraints cache

2324097 Virtuoso exits unexpectedly when launching Schematics XL

2324083 Virtuoso exits unexpectedly due to an internal application error

2323750 Padstacks are erroneously exported to CLF as bumps

2323703 Virtuoso exits unexpectedly due to a segmentation fault in ddtUpdateGraph in IC6.1.8 ISR12

2323562 Create Via command not following the correct purpose defined in layer1ExtraParams

2323534 Via not created by Auto Via command due to obstruction.

2323038 emir.conf file not written to the netlist directory for AMS EMIR run with the new EMIR UI

2322780 3X performance degradation observed during power grid generation as cover cell at initialization

2322703 5X performance degradation observed during power grid generation as FigGroup at initialization

2321972 The Chaining command takes up to 2 minutes to open the Options form

2321733 Virtuoso exits unexpectedly in ctuOaUpdate::registerOAShapeToBeDeleted

2321703 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321436 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321137 Virtuoso exits unexpectedly during Check and Save

2321080 Probe translation fails when device prefix is different for different devices of the same type

2319537 The Push Pre-Routes command ignores via blockages when there are floating wires in the design

2319127 Remove all instances of catch/throw from the code

2318879 Virtuoso exits unexpectedly when deleting labels in Text Editor

2317803 Virtuoso exits unexpectedly when using Design Intent

2317179 Checker does not consider full wire length to determine width direction when using the minOppExtension table

2316623 Auto Via command must reduce one edge by 1db to handle another offset correctly

2316506 Virtuoso exits unexpectedly when browsing Rapid Analog Prototype constraints

2316443 Unable to generate eadTechFile using the eadModelGen utility

2315205 minViaSpacing support for centerToCenter parameter does not work as expected

2314971 Expressions with extracted view net mapping in LSCS control mode evaluate into errors but evaluate successfully in ICRP mode

2314905 The simulation does not run on setting up a single individual fault in the ADE Assembler fault simulation setup

2314592 Virtuoso exits unexpectedly while processing a pop-up menu event

2313575 Improve handling of netlisting failures

2312572 Extractor claims there is no via definition with implant layer if extractVerifyWellSubstrateConnections is nil

2312347 Virtuoso exits unexpectedly after AMS Monte Carlo simulation completes

2312108 Updating library property bag using the FirstAccessLib trigger fails in ICADVM18.1

2311881 The Set Valid Layers form is distorted in IC6.1.8 but appears fine in IC6.1.7

2310932 Decap Fill places overlapping decaps

2309540 Add save statements for post layout signals used in expressions

2309431 Checker does not flag violations when using direction parameters with minOppExtension

2309277 Virtuoso exits unexpectedly during dbClose

2308056 Virtuoso exits unexpectedly during descend read

2307756 Virtuoso exits unexpectedly when saving constraints cache

2307603 A beta license is required to use the technology file in Voltus-Fi

2307296 Random netlist and simulation errors when run Size Over Corners

2306918 Incorrect pg_function exported for some pins

2306226 DesignSync options are ignored when creating a setup library view using the slaOpenOrCreateView function

2305135 Placement Planning throws an error when the Tap tab is hidden

2305117 SystemVerilog Netlister stops responding and causes Virtuoso to exit unexpectedly

2305014 Need an option to display all the active WSPs for a given layer

2304848 Virtuoso exits unexpectedly while cleaning up raw shape to fractured shapes mapping.

2304824 Virtuoso exits unexpectedly when saving constraints cache

2304346 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2303971 pg_function is not being detected correctly

2303856 Fault simulation with sampling fails because fault statement has incomplete sample option

2303636 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode.

2303616 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode

2303562 Trunk trim generate wrong begin and end point of a pathSeg

2303178 Virtuoso stops responding when using leHiAssignNet command and Repeat Command is off in the Layout Editor Options form

2303148 SystemVerilog Netlister stops responding when using time literals to override CDF parameters

2302634 Unable to generate an AMS netlist when using pPar function in the parameter values for the specified instances

2302553 The Voltus-Fi GUI does not load any nets in the EM results window when vsaSetEMPlot and vsaLoadNets functions are used together

2302343 Expression evaluates for failed iteration of Monte Carlo run in LSCS run mode

2301963 Many config views are created with config sweep by LSCS in ADE

2301789 Virtuoso exits unexpectedly when evaluating the spectrumMeasurement expression from ADE Assembler

2301775 Allegro Import translator generates errors in ECO mode when 'ocm' symbols exist in the SiP file

2301724 When separate history management is enabled, Virtuoso exits unexpectedly after copying a maestro view and deleting a history point

2301209 Enable the traceTxChainWithDirComp flag in vpmSetEnvVals()

2301206 Enable the extendedHierCellTermDirCheck flag in vpmSetEnvVals()

2301072 Parametric sweep fails with ERROR (ASSEMBLER-2343) using dependent variables

2300228 Parameter not set in the netlist when using calcVal and variable sweep in the corners

2299793 Handle automatically created RPP for single rail level shifter cells in Virtuoso Power Manager

2299786 Handle three-terminal devices in supply and data path in Virtuoso Power Manager extractor

2299778 Virtuoso Power Manager extractor to support three-terminal capacitor devices

2299767 Virtuoso Power Manager setup to support registration of three-terminal devices in the capacitor category

2299373 Virtuoso Power Manager missing pg_pin definition in the exported Liberty file

2299234 Virtuoso stops responding when using recursive variable in ADE Explorer

2299076 Virtuoso exits unexpectedly when non-static data members of a class are not initialized

2299013 Operating Region Violations option missing in the context menu of the Detail results view

2298616 Noise summary feature does not work as expected on specifying instances through the 'Include Instances' field

2298606 The Spectrum assistant rounds off stop time, giving wrong THD results and spectrum plot

2298548 FastC Coupled C becomes smaller when side metal is in a specific range

2298313 XOasis Out does not set strict flag for layerNames in OASIS files

2298035 Can we run Modelwriter in IC6.1.8 ISR12?

2297815 The clip function does not work with a family of voltage waveforms in the Monte Carlo simulation

2297684 Unable to launch Verify Design UI

2297489 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2296131 Virtuoso Power Manager extracting incorrect pg_function for a few pins

2296127 Virtuoso Power Manager missing pg_function for a few pins

2296004 Virtuoso Power Manager extracting incomplete pg_function

2295351 Virtuoso exits unexpectedly when specifying the setup data in Data View assistant

2294844 Slow performance when leHiFlatten command is run

2294441 The Auto Via command is choosing larger enclosure than expected for GM0 metal

2294333 pz analysis results are plotted in wrong axes

2294162 Filter issues for multiple corner model setup in Detail-Transpose results view

2293292 Virtuoso Power Manager is inheriting VDD/supply attribute from cells in the ignore category

2293289 Virtuoso Power Manager extractor does not contain pg_function values for few pins in scratch mode

2293284 Update the Noise Summary form in IC6.1.8 ISR7 to support wildcards when selecting instances with hierarchy in the schematic

2293277 Size Over Corners fails unless OK is clicked on the new Size Over Corners options form

2293273 Size Over Corners does not proceed with corner analysis

2292266 When editing virtual hierarchy, switch back to the workspace that customer used to work in Layout XL

2292256 Display all local nets up to the virtual pins within a virtual hierarchy when doing Select - Local Nets on a selected virtual hierarchy

2291881 Options on the Harmonic Balance Noise Analysis form do not display correctly when Noise Figure is selected

2291692 SKILL function ddsSetLibManLCV does not work on combined libraries

2291057 While accessing Self-Heating Effect analysis reports, on reverting back to text files from html files, the text files go missing

2290993 Checker exits unexpectedly if a layerIndex value for a layer specified with minVoltageExtension is 0

2290870 Virtuoso exits unexpectedly when attaching a technology database to a library

2290004 AMS UNL netlisting assembly does not work as expected in IC6.1.8 ISR10

2289577 Add model name to the exported Unified Power Format file

2289480 Performance is degraded during interactive edit operation for DI associated object

2288933 ADE Explorer allows adding temp in design variable

2288846 Virtuoso stops responding when using multiple tabs

2288273 ESD Optimizer removes vias that should be retained in the optimized DSPF file

2288267 The ESD HBM waveform shows an incorrect current value at t=0 that does not match the schematic value

2287209 ADE Verifier ignores the values in the Verification Space column when importing data from a CSV file

2286809 Unable to change order of the pin in Pin Tool after "Create Pin Template" utility is invoked.

2286617 Add the argument rcr=selected to the Solver Method table on selecting Iterated as the solver method

2286597 Pin Optimizer fails when there is a mosaic in the design

2286453 Links with literal equal sign (=) do not work with the hiCreateHypertextField

2286247 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2285890 Layout XL stops responding when using Gnome window manager

2284658 Provide the support to register any instance as header or footer type special cell

2284010 Additional argument 'Exclude' for net analysis in the ADE EMIR Setup form gets appended as a new line in the Summary Information table

2283915 Pre-simulation of an operating region spec is stopped when ADE Assembler uses a local host

2283485 DRD does not report minExtensionEdge constraint violations

2283273 A strange stdVia remains when we escape the command during wiring

2283202 Virtuoso Power Manager not extracting the expected isolation strategy signal

2283171 Additional internal power pins found for related power pins

2280242 Performance degradation observed when transitioning from ADE L to ADE Explorer

2279815 When working with the Make Cell operation, selected objects are losing connectivity

2279021 Virtuoso Space-based Router introduces maxWidth and allowedWidthRanges violations when hitting offGrid pins

2277658 Unable to create a via using the Auto Via command due to shape on cut layer though purpose of cut shape is specified in viaIgnorePurposes

2277395 The autoSave environment variable does not work in IC6.1.8 and ICADVM18.1 ISR9 or later releases

2277352 Found libImport errors in Allegro board file

2276459 DEFOUT of path objects adds unwanted horizontal extension at 45-degree transitions

2276436 Library copy must also update target and footprint library name parameters

2276425 Provide support for package footprint export of an imported SiP layout

2275830 The awvSetLegendWidth function does not work with circular graphs

2274889 Remove the Set Valid Layers form

2273262 Memory consumption increases when using noiseSummary() statement in the OCEAN script

2273154 AMS UNL netlister with arrayed instances in the SystemVerilog code causes an EXNEUS elaboration error.

2272602 Additional internal supplies in exported Liberty file

2272601 Virtuoso Power Manager missing pg_function for a few pins

2272060 Virtuoso exits unexpectedly due to segmentation fault in axlPlotSingleOutput

2271313 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2270877 Runams adds -flow argument to the probe.tcl file on restarting, which causes Spectre to fail

2270654 Update Components and Nets should replace existing pin in case Design Intent for that pin is updated to different layer or width

2269647 Support for module type in the Co-Design flow

2268969 Co-Design does not work if the fabric type is module

2264905 Extracting VerilogAMS cellviews stopped working since IC6.1.8 ISR6

2264534 Yield view shows incorrect results when using the VAR expression to define specifications

2263432 Line chop in minSpacing mode chops pathSeg placed outside prBoundary with larger value than required

2263427 Line chop in minSpacing mode does not chop rectangle placed outside prBoundary

2262620 Implicit signals are not generated because of a specific sequence of changing 'Save all' options

2262063 Spectre assert statements return 'inf' for Duration (%) in ADE Assembler output Checks/Asserts table

2259594 Virtuoso exits unexpectedly when running an EM simulation using a smart view

2259565 Smart view is not netlisted correctly; shows a warning that the view is not a valid extracted view

2259521 Layout XL: Incorrect extraction for a MIM capacitor in two-metal stack configuration

2258187 Double-clicking a signal waveform incorrectly works as the Plot All command

2255264 The 'filter_ir_percent' option does not work in Voltus-Fi

2254523 Update the *WARNING* (LCE-2045) message to reflect the actual type of the layer instead of using the term 'logical layer'

2253741 Setting the environment variable groupRunA to nil causes identical corner point runs to be linked and not rerun

2252419 The footprint Library Name property does not automatically update in Schematic Edit Object Properties

2246655 Performance issues when waiving more than 10k violations

2246026 Measurement across corners is not working correctly for expressions without name

2245814 ADE Explorer slower than ADE L when ignoreDesignChangesDuringRun is set

2244573 Virtuoso RF Solution: Instantiated pins are no longer visible after changing the name of the Export Die library

2243791 Allegro Import translation fails with SiPtoOA error

2237464 Virtuoso exits unexpectedly when pasting objects which include one or more traces

2237124 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

2236937 Virtuoso exits unexpectedly when using the Fit Visible Traces command

2235874 Modgen template reuse gives warning and fails

2235872 Virtuoso exits unexpectedly when running simulations in ADE Assembler

2232020 Virtuoso RF Solution viaSelectionMode use non-Cutlayers blocks via selection

2229395 Limiting voltage parameter in variableGainAmplifier in Functional Library does not work

2228879 Output expressions with plot and save disabled should not be evaluated

2222659 Discrepancy between spectre_ddmrpt and ADE assembler fault report

2222582 Appearance of statement aging_analysis_name value=dc in the netlist

2215721 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2213922 Router routes over blockages for some differential pair nets

2210847 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2208481 Model group name containing a dot (.) causes an error in worst case corners

2204742 Virtuoso exits unexpectedly when the hiRegZoomPanProc SKILL function is used

2203332 Spectre reliability relx_tran argument truncates decimal points

2200925 Reference History does not work as expected when using variables dependent on each other

2190802 Checks/Asserts tab reports 'inf' for Duration (%)

2188074 The rodFillBBoxWithRects SKILL function is creating fill shapes outside the given bounding box

2182019 In Pin to Trunk routing, Trunk Extend extends the trunk outside of selected area

2170762 ADE Assembler consumes large amounts of memory and does not release it until Virtuoso is closed

2150446 Pin Placement is creating shorts for existing power pins

2147838 SKILL function ddsSetLibManLCV does not work on combined libraries

2141130 Release memory after ADE Assembler is closed

2128122 The leGetCoordinateForm (bindkey Shift+N) Pan-to-coordinate is not compatible with infix mode

2112949 Discrepancies in the results displayed in Detail view and Yield view

2110671 Bug in waveform comparison across corner

2098875 Memory no longer needed by ADE Assembler should be released to OS

2067163 Memory consumed by ADE Assembler is not released when the tool is closed; need to close Virtuoso

2064375 Incremental netlisting does not work with AMS Designer in ADE Explorer

2035506 Typical implementation does not work with the model files that do not have section details

2025368 Incremental netlisting does not work with AMS Designer in ADE Explorer

2020300 Pin To Trunk routing chooses offset via for simple pattern

2007678 In ADE Assembler, the Create Test Copy command in the context menu of Corners does not copy enabled corners in the Corner Setup form

1994369 Creating a Test Copy does not copy the corners setup

1961784 Specifying a variable in the Relative Harmonic field in the Periodic Noise Analysis setup gives an error

1954211 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1928931 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1832041 SKILL function ddsSetLibManLCV does not work on combined libraries

1767782 Allow to waive corner-specific violations

918684 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

October 2020

2332071 Cannot change the test name in maestro view in ADE Explorer

2327724 The CSV file in which the setup is exported from the Results tab in ADE Assembler is not saved at the desired location

2327005 Wrong column header exporting CSV file from detail transpose

2326741 Virtuoso exits unexpectedly due to an internal application error

2326292 Running 'runsv' reports 'runams' instead of 'runsv'

2326286 Virtuoso exits unexpectedly when editing a figGroup

2325395 Create Via command violates shape boundary for polygonal shapes

2325056 Virtuoso exits unexpectedly when saving constraints cache

2324097 Virtuoso exits unexpectedly when launching Schematics XL

2324083 Virtuoso exits unexpectedly due to an internal application error

2323750 Padstacks are erroneously exported to CLF as bumps

2323703 Virtuoso exits unexpectedly due to a segmentation fault in ddtUpdateGraph in IC6.1.8 ISR12

2323562 Create Via command not following the correct purpose defined in layer1ExtraParams

2323534 Via not created by Auto Via command due to obstruction.

2323038 emir.conf file not written to the netlist directory for AMS EMIR run with the new EMIR UI

2322780 3X performance degradation observed during power grid generation as cover cell at initialization

2322703 5X performance degradation observed during power grid generation as FigGroup at initialization

2321972 The Chaining command takes up to 2 minutes to open the Options form

2321733 Virtuoso exits unexpectedly in ctuOaUpdate::registerOAShapeToBeDeleted

2321703 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321436 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321137 Virtuoso exits unexpectedly during Check and Save

2321080 Probe translation fails when device prefix is different for different devices of the same type

2319537 The Push Pre-Routes command ignores via blockages when there are floating wires in the design

2319127 Remove all instances of catch/throw from the code

2318879 Virtuoso exits unexpectedly when deleting labels in Text Editor

2317803 Virtuoso exits unexpectedly when using Design Intent

2317179 Checker does not consider full wire length to determine width direction when using the minOppExtension table

2316623 Auto Via command must reduce one edge by 1db to handle another offset correctly

2316506 Virtuoso exits unexpectedly when browsing Rapid Analog Prototype constraints

2316443 Unable to generate eadTechFile using the eadModelGen utility

2315205 minViaSpacing support for centerToCenter parameter does not work as expected

2314971 Expressions with extracted view net mapping in LSCS control mode evaluate into errors but evaluate successfully in ICRP mode

2314905 The simulation does not run on setting up a single individual fault in the ADE Assembler fault simulation setup

2314592 Virtuoso exits unexpectedly while processing a pop-up menu event

2313575 Improve handling of netlisting failures

2312572 Extractor claims there is no via definition with implant layer if extractVerifyWellSubstrateConnections is nil

2312347 Virtuoso exits unexpectedly after AMS Monte Carlo simulation completes

2312108 Updating library property bag using the FirstAccessLib trigger fails in ICADVM18.1

2311881 The Set Valid Layers form is distorted in IC6.1.8 but appears fine in IC6.1.7

2310932 Decap Fill places overlapping decaps

2309540 Add save statements for post layout signals used in expressions

2309431 Checker does not flag violations when using direction parameters with minOppExtension

2309277 Virtuoso exits unexpectedly during dbClose

2308056 Virtuoso exits unexpectedly during descend read

2307756 Virtuoso exits unexpectedly when saving constraints cache

2307603 A beta license is required to use the technology file in Voltus-Fi

2307296 Random netlist and simulation errors when run Size Over Corners

2306918 Incorrect pg_function exported for some pins

2306226 DesignSync options are ignored when creating a setup library view using the slaOpenOrCreateView function

2305135 Placement Planning throws an error when the Tap tab is hidden

2305117 SystemVerilog Netlister stops responding and causes Virtuoso to exit unexpectedly

2305014 Need an option to display all the active WSPs for a given layer

2304848 Virtuoso exits unexpectedly while cleaning up raw shape to fractured shapes mapping.

2304824 Virtuoso exits unexpectedly when saving constraints cache

2304346 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2303971 pg_function is not being detected correctly

2303856 Fault simulation with sampling fails because fault statement has incomplete sample option

2303636 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode.

2303616 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode

2303562 Trunk trim generate wrong begin and end point of a pathSeg

2303178 Virtuoso stops responding when using leHiAssignNet command and Repeat Command is off in the Layout Editor Options form

2303148 SystemVerilog Netlister stops responding when using time literals to override CDF parameters

2302634 Unable to generate an AMS netlist when using pPar function in the parameter values for the specified instances

2302553 The Voltus-Fi GUI does not load any nets in the EM results window when vsaSetEMPlot and vsaLoadNets functions are used together

2302343 Expression evaluates for failed iteration of Monte Carlo run in LSCS run mode

2301963 Many config views are created with config sweep by LSCS in ADE

2301789 Virtuoso exits unexpectedly when evaluating the spectrumMeasurement expression from ADE Assembler

2301775 Allegro Import translator generates errors in ECO mode when 'ocm' symbols exist in the SiP file

2301724 When separate history management is enabled, Virtuoso exits unexpectedly after copying a maestro view and deleting a history point

2301209 Enable the traceTxChainWithDirComp flag in vpmSetEnvVals()

2301206 Enable the extendedHierCellTermDirCheck flag in vpmSetEnvVals()

2301072 Parametric sweep fails with ERROR (ASSEMBLER-2343) using dependent variables

2300228 Parameter not set in the netlist when using calcVal and variable sweep in the corners

2299793 Handle automatically created RPP for single rail level shifter cells in Virtuoso Power Manager

2299786 Handle three-terminal devices in supply and data path in Virtuoso Power Manager extractor

2299778 Virtuoso Power Manager extractor to support three-terminal capacitor devices

2299767 Virtuoso Power Manager setup to support registration of three-terminal devices in the capacitor category

2299373 Virtuoso Power Manager missing pg_pin definition in the exported Liberty file

2299234 Virtuoso stops responding when using recursive variable in ADE Explorer

2299076 Virtuoso exits unexpectedly when non-static data members of a class are not initialized

2299013 Operating Region Violations option missing in the context menu of the Detail results view

2298616 Noise summary feature does not work as expected on specifying instances through the 'Include Instances' field

2298606 The Spectrum assistant rounds off stop time, giving wrong THD results and spectrum plot

2298548 FastC Coupled C becomes smaller when side metal is in a specific range

2298313 XOasis Out does not set strict flag for layerNames in OASIS files

2298035 Can we run Modelwriter in IC6.1.8 ISR12?

2297815 The clip function does not work with a family of voltage waveforms in the Monte Carlo simulation

2297684 Unable to launch Verify Design UI

2297489 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2296131 Virtuoso Power Manager extracting incorrect pg_function for a few pins

2296127 Virtuoso Power Manager missing pg_function for a few pins

2296004 Virtuoso Power Manager extracting incomplete pg_function

2295351 Virtuoso exits unexpectedly when specifying the setup data in Data View assistant

2294844 Slow performance when leHiFlatten command is run

2294441 The Auto Via command is choosing larger enclosure than expected for GM0 metal

2294333 pz analysis results are plotted in wrong axes

2294162 Filter issues for multiple corner model setup in Detail-Transpose results view

2293292 Virtuoso Power Manager is inheriting VDD/supply attribute from cells in the ignore category

2293289 Virtuoso Power Manager extractor does not contain pg_function values for few pins in scratch mode

2293284 Update the Noise Summary form in IC6.1.8 ISR7 to support wildcards when selecting instances with hierarchy in the schematic

2293277 Size Over Corners fails unless OK is clicked on the new Size Over Corners options form

2293273 Size Over Corners does not proceed with corner analysis

2292266 When editing virtual hierarchy, switch back to the workspace that customer used to work in Layout XL

2292256 Display all local nets up to the virtual pins within a virtual hierarchy when doing Select - Local Nets on a selected virtual hierarchy

2291881 Options on the Harmonic Balance Noise Analysis form do not display correctly when Noise Figure is selected

2291692 SKILL function ddsSetLibManLCV does not work on combined libraries

2291057 While accessing Self-Heating Effect analysis reports, on reverting back to text files from html files, the text files go missing

2290993 Checker exits unexpectedly if a layerIndex value for a layer specified with minVoltageExtension is 0

2290870 Virtuoso exits unexpectedly when attaching a technology database to a library

2290004 AMS UNL netlisting assembly does not work as expected in IC6.1.8 ISR10

2289577 Add model name to the exported Unified Power Format file

2289480 Performance is degraded during interactive edit operation for DI associated object

2288933 ADE Explorer allows adding temp in design variable

2288846 Virtuoso stops responding when using multiple tabs

2288273 ESD Optimizer removes vias that should be retained in the optimized DSPF file

2288267 The ESD HBM waveform shows an incorrect current value at t=0 that does not match the schematic value

2287209 ADE Verifier ignores the values in the Verification Space column when importing data from a CSV file

2286809 Unable to change order of the pin in Pin Tool after "Create Pin Template" utility is invoked.

2286617 Add the argument rcr=selected to the Solver Method table on selecting Iterated as the solver method

2286597 Pin Optimizer fails when there is a mosaic in the design

2286453 Links with literal equal sign (=) do not work with the hiCreateHypertextField

2286247 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2285890 Layout XL stops responding when using Gnome window manager

2284658 Provide the support to register any instance as header or footer type special cell

2284010 Additional argument 'Exclude' for net analysis in the ADE EMIR Setup form gets appended as a new line in the Summary Information table

2283915 Pre-simulation of an operating region spec is stopped when ADE Assembler uses a local host

2283485 DRD does not report minExtensionEdge constraint violations

2283273 A strange stdVia remains when we escape the command during wiring

2283202 Virtuoso Power Manager not extracting the expected isolation strategy signal

2283171 Additional internal power pins found for related power pins

2280242 Performance degradation observed when transitioning from ADE L to ADE Explorer

2279815 When working with the Make Cell operation, selected objects are losing connectivity

2279021 Virtuoso Space-based Router introduces maxWidth and allowedWidthRanges violations when hitting offGrid pins

2277658 Unable to create a via using the Auto Via command due to shape on cut layer though purpose of cut shape is specified in viaIgnorePurposes

2277395 The autoSave environment variable does not work in IC6.1.8 and ICADVM18.1 ISR9 or later releases

2277352 Found libImport errors in Allegro board file

2276459 DEFOUT of path objects adds unwanted horizontal extension at 45-degree transitions

2276436 Library copy must also update target and footprint library name parameters

2276425 Provide support for package footprint export of an imported SiP layout

2275830 The awvSetLegendWidth function does not work with circular graphs

2274889 Remove the Set Valid Layers form

2273262 Memory consumption increases when using noiseSummary() statement in the OCEAN script

2273154 AMS UNL netlister with arrayed instances in the SystemVerilog code causes an EXNEUS elaboration error.

2272602 Additional internal supplies in exported Liberty file

2272601 Virtuoso Power Manager missing pg_function for a few pins

2272060 Virtuoso exits unexpectedly due to segmentation fault in axlPlotSingleOutput

2271313 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2270877 Runams adds -flow argument to the probe.tcl file on restarting, which causes Spectre to fail

2270654 Update Components and Nets should replace existing pin in case Design Intent for that pin is updated to different layer or width

2269647 Support for module type in the Co-Design flow

2268969 Co-Design does not work if the fabric type is module

2264905 Extracting VerilogAMS cellviews stopped working since IC6.1.8 ISR6

2264534 Yield view shows incorrect results when using the VAR expression to define specifications

2263432 Line chop in minSpacing mode chops pathSeg placed outside prBoundary with larger value than required

2263427 Line chop in minSpacing mode does not chop rectangle placed outside prBoundary

2262620 Implicit signals are not generated because of a specific sequence of changing 'Save all' options

2262063 Spectre assert statements return 'inf' for Duration (%) in ADE Assembler output Checks/Asserts table

2259594 Virtuoso exits unexpectedly when running an EM simulation using a smart view

2259565 Smart view is not netlisted correctly; shows a warning that the view is not a valid extracted view

2259521 Layout XL: Incorrect extraction for a MIM capacitor in two-metal stack configuration

2258187 Double-clicking a signal waveform incorrectly works as the Plot All command

2255264 The 'filter_ir_percent' option does not work in Voltus-Fi

2254523 Update the *WARNING* (LCE-2045) message to reflect the actual type of the layer instead of using the term 'logical layer'

2253741 Setting the environment variable groupRunA to nil causes identical corner point runs to be linked and not rerun

2252419 The footprint Library Name property does not automatically update in Schematic Edit Object Properties

2246655 Performance issues when waiving more than 10k violations

2246026 Measurement across corners is not working correctly for expressions without name

2245814 ADE Explorer slower than ADE L when ignoreDesignChangesDuringRun is set

2244573 Virtuoso RF Solution: Instantiated pins are no longer visible after changing the name of the Export Die library

2243791 Allegro Import translation fails with SiPtoOA error

2237464 Virtuoso exits unexpectedly when pasting objects which include one or more traces

2237124 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

2236937 Virtuoso exits unexpectedly when using the Fit Visible Traces command

2235874 Modgen template reuse gives warning and fails

2235872 Virtuoso exits unexpectedly when running simulations in ADE Assembler

2232020 Virtuoso RF Solution viaSelectionMode use non-Cutlayers blocks via selection

2229395 Limiting voltage parameter in variableGainAmplifier in Functional Library does not work

2228879 Output expressions with plot and save disabled should not be evaluated

2222659 Discrepancy between spectre_ddmrpt and ADE assembler fault report

2222582 Appearance of statement aging_analysis_name value=dc in the netlist

2215721 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2213922 Router routes over blockages for some differential pair nets

2210847 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2208481 Model group name containing a dot (.) causes an error in worst case corners

2204742 Virtuoso exits unexpectedly when the hiRegZoomPanProc SKILL function is used

2203332 Spectre reliability relx_tran argument truncates decimal points

2200925 Reference History does not work as expected when using variables dependent on each other

2190802 Checks/Asserts tab reports 'inf' for Duration (%)

2188074 The rodFillBBoxWithRects SKILL function is creating fill shapes outside the given bounding box

2182019 In Pin to Trunk routing, Trunk Extend extends the trunk outside of selected area

2170762 ADE Assembler consumes large amounts of memory and does not release it until Virtuoso is closed

2150446 Pin Placement is creating shorts for existing power pins

2147838 SKILL function ddsSetLibManLCV does not work on combined libraries

2141130 Release memory after ADE Assembler is closed

2128122 The leGetCoordinateForm (bindkey Shift+N) Pan-to-coordinate is not compatible with infix mode

2112949 Discrepancies in the results displayed in Detail view and Yield view

2110671 Bug in waveform comparison across corner

2098875 Memory no longer needed by ADE Assembler should be released to OS

2067163 Memory consumed by ADE Assembler is not released when the tool is closed; need to close Virtuoso

2064375 Incremental netlisting does not work with AMS Designer in ADE Explorer

2035506 Typical implementation does not work with the model files that do not have section details

2025368 Incremental netlisting does not work with AMS Designer in ADE Explorer

2020300 Pin To Trunk routing chooses offset via for simple pattern

2007678 In ADE Assembler, the Create Test Copy command in the context menu of Corners does not copy enabled corners in the Corner Setup form

1994369 Creating a Test Copy does not copy the corners setup

1961784 Specifying a variable in the Relative Harmonic field in the Periodic Noise Analysis setup gives an error

1954211 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1928931 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1832041 SKILL function ddsSetLibManLCV does not work on combined libraries

1767782 Allow to waive corner-specific violations

918684 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

October 2020

2551574 Tcl files already specified in the setup are not being passed to xrun in ICADVM20.1 ISR19

2549449 Virtuoso exits unexpectedly with assertion failure in ABE

2548865 oaScan fails if cds.lib is not located in current working directory during the Design Integrity check in Performance Diagnosis

2548826 A Monte Carlo run ignores the config sweep settings in ICRP job control mode

2548061 Config sweeps do not get netlisted again when the variables simReNetlistAll and nlReNetlistAll are set to nil in the .simrc file

2547445 Stacked config sweep picking up wrong cellview

2545788 Incorrect status of jobs is shown in Run Summary when using LSCS

2545179 DRD check clean not returning violation markers for maxViaArrayClusterSize with maxFacingEdgeNeighbors

2544389 Virtuoso exits unexpectedly when the Mark Net command is used

2543251 Virtuoso exits unexpectedly on routing a net in a customer testcase

2542488 Allegro Import translator fails when used with 'Generate Instances as in Schematic'

2542305 Pin order mismatch between instance and subckt in ICRP netlist

2541686 Allegro Import translator fails with 'strcat' error

2541425 Mismatch in number of VSync shapes created in ICADVM20.1 ISR19 and ICADVM20.1.ISR20

2541012 Concurrent Layout exits unexpectedly when editing in a design partition with internal errors

2540781 Allow terminal voltage probing when preserveSubcktTermNamesByOrder is set to t

2540117 Allegro Import fails when used with 'Generate instance as in Schematic' to make a design Virtuoso RF compatible

2539323 Virtuoso exits unexpectedly with error mapiMngr::deleteSession

2539172 Idle jobs block launching of next simulation

2539079 Virtuoso Power Manager to improve the exported expression by removing additional or unwanted elements and objects

2538201 Virtuoso Power Manager: Add support for identifying name-based Charge Device Model cells

2538082 Virtuoso Power Manager exits unexpectedly for a design

2537865 Some netlists are not correctly linked to .tmpADEDir; thereby causing simulation issues and showing menu of ICRP in LSCS

2537561 After making a change in the HED, running an AMS simulation in ADE Explorer results in a UNL netlist error

2536729 mptColorRemastering() command does not work in Virtuoso nograph mode

2536560 Wires accidentally deleted during check&save

2535540 Unable to run the Pin to Trunk command in ICADVM20.1 ISR18

2535436 During Allegro Import translation slivers of dynamic shapes are left behind creating false shorts

2535380 Userdv shape is not created on top level shapes.

2534450 Virtuoso stops responding while running ocnPrintTMIReliabilityResults()

2533235 auCDL does not netlist properly in IC6.1.8 ISR19

2533197 Error in phoWayPointConnector due to undefined variables

2533094 Reliability Report: In case of large netlists, ADE Assembler stop responding after age simulation has completed

2531906 Virtuoso Power Manager: User-defined macro flow missing switch pin and switched power in the exported Liberty file

2531902 Virtuoso Power Manager: User-defined macro flow changes for the switch pin attribute

2531875 Distributed netlist jobs linger for 300 seconds due to Start Timeout

2531761 In Concurrent Layout a synchronous copy in a design partition conflicts with same name object in other design partition

2531255 Remove inversion from the pg_function for virtual ground pg pins

2531227 Change in voltage map after user-defined macro registration

2531222 Switch pin attribute missing after user-defined macro registration

2531219 Switch function missing after user-defined macro registration for one of the pins

2531218 Switch cell type missing after user-defined macro registration

2531001 Incorrect netlist generation on running a device parameter sweep with a config sweep

2530920 Stretch command is leaving behind associated vias when KeepWiresConnectedToShape mode is selected

2530828 Sanity Checker, label vs dataset, is not checking worst case dataset value based on all the dataset selection

2529940 CDLOUT produces netlist with instance parameter missing from the diode defining statement

2529461 Virtuoso exits unexpectedly in tpaSetActivePattern()

2529330 Virtuoso exits unexpectedly when 'Update Components and Nets' is run in Virtuoso Layout Suite XL to update the pins

2529159 The auto twig functionality in simulation-driven interactive routing places vias but fails to connect some of the cells

2529141 Extremely slow copy of test through the Create Test Copy command

2529117 After migration to ICADVM20.1 ISR19, Tcl files already specified in the setup are ignored by the simulator

2527883 Virtuoso RF Solution needs a Read-in-Concert functionality

2527643 Idle netlister jobs will start shell process to touch a file

2527598 When using LSCS for a run plan, some points need to wait for a long time for job assignment

2527376 Icons in collapsed toolbars not working

2527189 cstGetFoundryConstraintGroup error displays a warning message for fluid guard ring during Quantus extraction run

2526977 isInterface check for bus terminals is not working properly

2526456 When S-Parameter analysis is used, Direct Plot adds a white space after the expression name in the outputs

2526371 Digital signals cannot be plotted during an ongoing AMS simulation

2526345 In-design checks: Sub-hierarchical in-design checks run uses high memory consumption

2526343 In-design checks feature printing repeated warning messages in the log file

2526341 In-design checks run on sub-cell taking too long to run

2526097 The Mark Net command has incorrect highlight result

2525730 Virtuoso exits unexpectedly when Edit – Hierarchy – Check command is run, and value of reference library is long

2525629 Virtuoso Power Manager is not tracing pg function for internal powers

2525616 Virtuoso Power Manager is consuming high memory for designs

2525563 The 'Enable Encryption' option in the Virtuoso AMS IP Export Reuse flow encrypts only the top-level netlist

2525394 Run Preview does not honor point selection

2525172 EM assistant Preview EM model is not working for Clarity model setting

2525100 Batch extractions needs to be run two times to locate the shorts

2525089 Virtuoso Power Manager printed backtick character as hierarchy separator in a few cases in the exported Liberty file

2524729 Virtuoso exits unexpectedly while evaluating a point

2524714 Spectre monitor gets stuck with the MPS error message

2524069 Distributed job launched on SGE remains in pending status

2523787 Failed to map schematic to smart view stitching errors for an LVS clean layout

2523651 xFGR Support for Metal and contact minOppExtension

2523485 Make sure the design netlist is reused for the runs in the run plan

2523482 Make sure design netlists are reused on tests with the same design even when calcVal is used

2523397 Running an AMS simulation without the MTS settings results in an error

2523179 Cannot use application name 'Layout XL' when leGetAllApplicationNames is used with deGetLowerTierApp

2523034 Netlisting service gets stuck when receiving an invalid message

2522992 An error message is displayed on running Wireless Analysis

2522441 Extracting objects only on the top hierarchy (Hierarchy Levels = 0) does not work as expected

2522347 In ICADVM20.1 ISR19, Virtuoso Space-based Router leaves some opens while bus routing

2522187 DesignSync design management environment for die export does not check out all the necessary view or files

2522150 leReportTrimmedShapesInCustomStyle does not report violations for missing pathSegs abutting trim shapes in same cellview

2521943 GFS virtual hierarchy area boundary generated by utilization percentage for all levels creates device overlaps

2521819 Make sure the design netlist is reused if the same DUT is used for the runs in a run plan

2521798 Spectre monitor cache problem is leading to a long evaluation time

2521786 Ensure that LSCS follows ignoreDesignChangesDuringRun strictly, even for run plan and other cases

2521784 Virtuoso exits unexpectedly for a run plan testcase before netlisting jobs get started

2521671 Virtuoso exits unexpectedly when trying to connect to beanstalk

2521668 Preview options are modified when the preview state is checked

2520471 Optimize point netlisting time

2519965 Virtuoso RF Solution-EMX: Preview EM Layout Issue

2519886 Property Editor fails to modify properties when multiple objects are selected

2519616 ?getFirstSweepPoint does not work for local sweeps with multiple calcVal dependencies

2519205 Digital signals cannot be plotted during an ongoing AMS simulation

2519093 For vmtLibImport, library check in/out should also perform check in/out for all the available files

2518941 The ICRP job control mode does not work with the new history management system in ADE Assembler

2518865 In ICADVM20.1, Virtuoso Space-based Router routes partially

2518813 Provide correct setup prompt when single simulation SHE flow is enabled or disabled

2518298 When running slotbyNet, sltShapeConsecutiveSlotting slots vias which do not belong to list of objects to be slotted

2517879 leLayerAndNot gives different result in IC6.1.8 ISR11 and IC6.1.8 ISR18

2517740 vmtLibImport needs to handle and update part.csv under design management environment properly

2517077 Retain the manual setting +postlpreset=OFF in the GUI when switching between presets

2516787 Point netlisting takes very long time in the DSPF flow

2516371 In hiCreateToggleField, enabledItems is not in sync with enabled attribute

2514702 Delete AGR and Fill option is not displayed in the context menu for merged AGRs

2514129 During concurrent layout editing path segment becomes longer after split if its end segment is outside design partition

2514111 Virtuoso exits unexpectedly: vvSetCurrentWindow after ddtUpdateGraph

2513933 Placement of instances is scattered when virtual hierarchy area boundary is stretched

2513420 If one side of an object is less than or equal to partition area halo, then this side of the object is not split

2513416 Temperature color map at stop time of transient is not displayed

2513400 In a design partition with multiple area boundaries 'Split Object Crossing Partitions' works only for one of them

2513280 LVS fails when the diffstbprobe component is removed from the netlist but not shorted like a voltage source

2513057 The SystemVerilog Netlister creates a netlist with multiple wire declarations resulting in compilation errors

2512989 Double RMB click bindkey for context menu does not work

2512819 Quantus transfer property functionality is missing multi-cell placed device properties

2512655 Netlister is not netlisting VAR expression correctly for some of the points

2512646 Point netlisting takes very long time when the DSPF flow is used

2511466 Digital signals cannot be plotted during an ongoing AMS simulation

2511462 Running an AMS simulation with a single SystemVerilog block gives an *E,WKLNDF error during netlisting

2511239 Bumps alignment check fails after bumps are propagated

2511164 Virtuoso stops responding during Discard Edits when edits are done across multiple tabs

2510116 Virtuoso exits unexpectedly when axlShowHideOutputSetupNamedFilterItems is run

2509633 Error if signal is plotted from HB analysis

2509607 AMS UNL flow gives an error on changing the config view; error points to the Pcell variant

2509111 ADE XL to maestro conversion causing AMS elaboration error for iterated instance varactors

2509013 Virtuoso exits unexpectedly when running EM analysis on a setup using qrcTechFile and emDataFile

2508640 Digital signals cannot be plotted when running simulations from ADE Assembler

2507631 After running an AMS simulation in ADE Assembler, viewing the netlist results in the readTable error

2507458 Virtuoso becomes unresponsive when using the 'Auto adjust area boundary' option with width and utilization

2506956 Error ADE 5019 is reported when trying to disable hysteresis DC analysis in Multi-Test Editor

2506943 Logical trace net bypasses trim layers

2506474 Virtuoso toolbars with extend button do not work properly when using the XFCE desktop

2506416 AMS fault simulation does not work with config DUT

2505856 Virtuoso toolbars with extend button do not work properly when using the XFCE desktop

2503270 Performance diagnosis for library shows 'ldap' server path. Need clarification on what it means

2503215 Layout editing on package level is slow even when extractVerifyInvalidConnections set to nil

2502219 sigType of existing nets and pins change when the sigType of a new net is changed

2502216 A tiny step is generated when a path object split during concurrent layout editing is stretched

2500960 Virtuoso RF: Simulation stops with an incorrect error when mixed sampling type is used for an EMX model

2500494 Results merge with run point selection does not work correctly when clicking the blue run button

2499019 Physical point at which the second event triggers is altered by shapes not related to abutment

2498627 allowedSpacingRanges is not flagging some violations with tapered widths

2497438 Allow the user to set their own EMX settings in UI

2496830 Virtuoso Power Manager does not extract Antennae Diode Related Power Pin for dummy and is always off for devices

2495332 The Compare & Merge flow does not detect deleted rows from a CSV or Microsoft Excel file

2494577 Two area boundaries are generated when pressing Enter key to finish specifying the partition area

2493583 define_signal_attributes do not handle power sniffer circuits having tx gate controls with feedback loop

2493564 Virtuoso Power Manager user-defined macro testing: Switch function and related ground pin change

2492636 DRD check clean is not returning violation markers for maxViaArrayClusterSize with maxFacingEdgeNeighbors

2491689 Display a warning when odd multiple width in a netClass would cause Virtuoso Space-based Router to route offGrid

2491665 Results view shows incorrect values while scrolling

2491480 The Reference Histories form in ADE Assembler does not allow selection of pending simulations

2491054 The 'DC Operating Points' option is greyed out on using Schematic Annotation in Virtuoso

2490528 hiCloseWindow segmentation faults in processOpenCVHasOAException

2488358 Improve via alignment when a minQuadrupleExtension constraint generates an asymmetric via not contained in the overlap

2487607 Running an AMS simulation with a single SystemVerliog block gives an *E,WKLNDF error during netlisting

2485447 Pin net collision after pin name change with new extractor

2483407 axlSetHistoryPrefixInPreRunTrigger allows invalid history names

2483353 Setting the temperature value in the Setting Temperature form clears the temperature specified in the Corners Setup form

2481278 Cannot deselect a trace family by clicking in the background

2481275 Cannot toggle the trace visibility for a trace family by using the context menu

2480612 Search in Data View is slow as it searches all the setup states

2476342 Descend edit for config view does not open schematic view

2467268 Run status shows pending and shows the 'Error while configuring the job' message in job log

2465667 Virtuoso exits unexpectedly due to segmentation fault in hiRaiseWindow

2459654 Signals are not plotted in the Results Browser when running an AMS simulation

2453440 Results view shows incorrect values while scrolling

2450149 In ADE Assembler, results filtering is canceled after interactive toggling of tabs in the Results view

2443148 Export Die will export matching the instance terminal and not the pins on the instance

2442967 Virtuoso stops responding when opening waveforms in Virtuoso Visualization and Analysis XL

2441236 Buttons get removed from the Models column when Reset is clicked after filtering in MTS Options form

2441227 In MTS Options form, clicking Update after adding filters for Library and Cell adds extra rows and extra buttons

2439330 Pin error when generating em_solver extracted view because of schSnapSpacing

2436453 ADE Assembler stops responding for a long time after the column width is auto adjusted if the Results table is bigger than the window size

2435642 Allow canceling of the ADE Assembler Save Setup question that is shown when exiting Virtuoso

2428192 Get 'Ineffective Global Job Policy' pop-up when changing job policy for a maestro view with no tests defined

2427600 Add a placement lock to figGroups

2422944 Calculator gives incorrect results after evaluating the expressions in the Buffer

2420690 hiSetCurrentWinNum segmentation faults

2412237 Properties of ROD multipart path objects not edited as expected when using SKILL

2399151 Virtuoso exits unexpectedly when modifying a multipart path

2399138 Global Signals form does not save changes to existing settings

2295871 All forms are pulled to the foreground when Edit Properties form is invoked in RHEL6 in IC6.1.8 ISR11 and ISR12

2295279 After AMS simulation, plotting a current signal directly from ADE XL shows the WIA-1006 error in CIW

2272466 During fill insertion, add an option to fill neighboring OD shapes belonging to the same row

2255542 Issues in the 'Select Tests are Displayed in Table' list on the Results tab after using the Plot Signal command

2253084 After a post-layout simulation with a DSPF file, unable to plot current data from ADE Assembler, but can plot the same from Results Browser

2249702 Allow signal type check between symbol pin and corresponding schematic pin on same cell

2246134 SKILL function awvPlotExpression gives error for AMS simulations in IC6.1.8; worked fine before

2241695 The 'Select which tests are displayed in table' filter shows all the listed tests as checked even if simulation is not run for all tests

2224397 When the -env ade runSimulation option is used in IC6.1.8, the current expression is different from the one that was added in IC6.1.7

2222105 After running a Spectre APS Monte Carlo simulation with a DSPF cellview, eval error is shown for an IT expression with a node current

2215367 Allow cross-view checker to check for signal type

2214529 Icons in collapsed toolbars are not working

2178982 For external text views, terminal current cannot be saved or plotted due to the '-env ade' argument

2062154 EAD cannot extract a resistance when 'Extraction Mode' is set to 'RC coupled'

2026432 Incorrect well merging because wells are hardcoded to connected 'B' terminals

2014147 Need a cross-view check for sigType property

1994353 Virtuoso stops responding when opening waveforms in Virtuoso Visualization and Analysis XL

1825696 Make sure the design netlist is reused if the same DUT is used for all runs in a run plan

1700431 In ADE Assembler, results filtering is canceled after interactive toggling of tabs in the Results view

1441002 Enhance Cross-View Checker in Layout L to prompt sigType mismatches across views

1147114 Add capability in Cross-View Check to check mismatch of signal type

862348 Check must enforce the same sigType values on pins of the schematic cross views

October 2021

2549449 Virtuoso exits unexpectedly with assertion failure in ABE

2548865 oaScan fails if cds.lib is not located in current working directory during the Design Integrity check in Performance Diagnosis

2548826 A Monte Carlo run ignores the config sweep settings in ICRP job control mode

2548061 Config sweeps do not get netlisted again when the variables simReNetlistAll and nlReNetlistAll are set to nil in the .simrc file

2547445 Stacked config sweep picking up wrong cellview

2545788 Incorrect status of jobs is shown in Run Summary when using LSCS

2545179 DRD check clean not returning violation markers for maxViaArrayClusterSize with maxFacingEdgeNeighbors

2544389 Virtuoso exits unexpectedly when the Mark Net command is used

2543251 Virtuoso exits unexpectedly on routing a net in a customer testcase

2542488 Allegro Import translator fails when used with 'Generate Instances as in Schematic'

2542305 Pin order mismatch between instance and subckt in ICRP netlist

2541686 Allegro Import translator fails with 'strcat' error

2541425 Mismatch in number of VSync shapes created in ICADVM20.1 ISR19 and ICADVM20.1.ISR20

2541012 Concurrent Layout exits unexpectedly when editing in a design partition with internal errors

2540781 Allow terminal voltage probing when preserveSubcktTermNamesByOrder is set to t

2540117 Allegro Import fails when used with 'Generate instance as in Schematic' to make a design Virtuoso RF compatible

2539323 Virtuoso exits unexpectedly with error mapiMngr::deleteSession

2539172 Idle jobs block launching of next simulation

2539079 Virtuoso Power Manager to improve the exported expression by removing additional or unwanted elements and objects

2538201 Virtuoso Power Manager: Add support for identifying name-based Charge Device Model cells

2538082 Virtuoso Power Manager exits unexpectedly for a design

2537865 Some netlists are not correctly linked to .tmpADEDir; thereby causing simulation issues and showing menu of ICRP in LSCS

2537561 After making a change in the HED, running an AMS simulation in ADE Explorer results in a UNL netlist error

2536729 mptColorRemastering() command does not work in Virtuoso nograph mode

2536560 Wires accidentally deleted during check&save

2535540 Unable to run the Pin to Trunk command in ICADVM20.1 ISR18

2535436 During Allegro Import translation slivers of dynamic shapes are left behind creating false shorts

2535380 Userdv shape is not created on top level shapes.

2534450 Virtuoso stops responding while running ocnPrintTMIReliabilityResults()

2533235 auCDL does not netlist properly in IC6.1.8 ISR19

2533197 Error in phoWayPointConnector due to undefined variables

2533094 Reliability Report: In case of large netlists, ADE Assembler stop responding after age simulation has completed

2531906 Virtuoso Power Manager: User-defined macro flow missing switch pin and switched power in the exported Liberty file

2531902 Virtuoso Power Manager: User-defined macro flow changes for the switch pin attribute

2531875 Distributed netlist jobs linger for 300 seconds due to Start Timeout

2531761 In Concurrent Layout a synchronous copy in a design partition conflicts with same name object in other design partition

2531255 Remove inversion from the pg_function for virtual ground pg pins

2531227 Change in voltage map after user-defined macro registration

2531222 Switch pin attribute missing after user-defined macro registration

2531219 Switch function missing after user-defined macro registration for one of the pins

2531218 Switch cell type missing after user-defined macro registration

2531001 Incorrect netlist generation on running a device parameter sweep with a config sweep

2530920 Stretch command is leaving behind associated vias when KeepWiresConnectedToShape mode is selected

2530828 Sanity Checker, label vs dataset, is not checking worst case dataset value based on all the dataset selection

2529940 CDLOUT produces netlist with instance parameter missing from the diode defining statement

2529461 Virtuoso exits unexpectedly in tpaSetActivePattern()

2529330 Virtuoso exits unexpectedly when 'Update Components and Nets' is run in Virtuoso Layout Suite XL to update the pins

2529159 The auto twig functionality in simulation-driven interactive routing places vias but fails to connect some of the cells

2529141 Extremely slow copy of test through the Create Test Copy command

2529117 After migration to ICADVM20.1 ISR19, Tcl files already specified in the setup are ignored by the simulator

2527883 Virtuoso RF Solution needs a Read-in-Concert functionality

2527643 Idle netlister jobs will start shell process to touch a file

2527598 When using LSCS for a run plan, some points need to wait for a long time for job assignment

2527376 Icons in collapsed toolbars not working

2527189 cstGetFoundryConstraintGroup error displays a warning message for fluid guard ring during Quantus extraction run

2526977 isInterface check for bus terminals is not working properly

2526456 When S-Parameter analysis is used, Direct Plot adds a white space after the expression name in the outputs

2526371 Digital signals cannot be plotted during an ongoing AMS simulation

2526345 In-design checks: Sub-hierarchical in-design checks run uses high memory consumption

2526343 In-design checks feature printing repeated warning messages in the log file

2526341 In-design checks run on sub-cell taking too long to run

2526097 The Mark Net command has incorrect highlight result

2525730 Virtuoso exits unexpectedly when Edit – Hierarchy – Check command is run, and value of reference library is long

2525629 Virtuoso Power Manager is not tracing pg function for internal powers

2525616 Virtuoso Power Manager is consuming high memory for designs

2525563 The 'Enable Encryption' option in the Virtuoso AMS IP Export Reuse flow encrypts only the top-level netlist

2525394 Run Preview does not honor point selection

2525172 EM assistant Preview EM model is not working for Clarity model setting

2525100 Batch extractions needs to be run two times to locate the shorts

2525089 Virtuoso Power Manager printed backtick character as hierarchy separator in a few cases in the exported Liberty file

2524729 Virtuoso exits unexpectedly while evaluating a point

2524714 Spectre monitor gets stuck with the MPS error message

2524069 Distributed job launched on SGE remains in pending status

2523787 Failed to map schematic to smart view stitching errors for an LVS clean layout

2523651 xFGR Support for Metal and contact minOppExtension

2523485 Make sure the design netlist is reused for the runs in the run plan

2523482 Make sure design netlists are reused on tests with the same design even when calcVal is used

2523397 Running an AMS simulation without the MTS settings results in an error

2523179 Cannot use application name 'Layout XL' when leGetAllApplicationNames is used with deGetLowerTierApp

2523034 Netlisting service gets stuck when receiving an invalid message

2522992 An error message is displayed on running Wireless Analysis

2522441 Extracting objects only on the top hierarchy (Hierarchy Levels = 0) does not work as expected

2522347 In ICADVM20.1 ISR19, Virtuoso Space-based Router leaves some opens while bus routing

2522187 DesignSync design management environment for die export does not check out all the necessary view or files

2522150 leReportTrimmedShapesInCustomStyle does not report violations for missing pathSegs abutting trim shapes in same cellview

2521943 GFS virtual hierarchy area boundary generated by utilization percentage for all levels creates device overlaps

2521819 Make sure the design netlist is reused if the same DUT is used for the runs in a run plan

2521798 Spectre monitor cache problem is leading to a long evaluation time

2521786 Ensure that LSCS follows ignoreDesignChangesDuringRun strictly, even for run plan and other cases

2521784 Virtuoso exits unexpectedly for a run plan testcase before netlisting jobs get started

2521671 Virtuoso exits unexpectedly when trying to connect to beanstalk

2521668 Preview options are modified when the preview state is checked

2520471 Optimize point netlisting time

2519965 Virtuoso RF Solution-EMX: Preview EM Layout Issue

2519886 Property Editor fails to modify properties when multiple objects are selected

2519616 ?getFirstSweepPoint does not work for local sweeps with multiple calcVal dependencies

2519205 Digital signals cannot be plotted during an ongoing AMS simulation

2519093 For vmtLibImport, library check in/out should also perform check in/out for all the available files

2518941 The ICRP job control mode does not work with the new history management system in ADE Assembler

2518865 In ICADVM20.1, Virtuoso Space-based Router routes partially

2518813 Provide correct setup prompt when single simulation SHE flow is enabled or disabled

2518298 When running slotbyNet, sltShapeConsecutiveSlotting slots vias which do not belong to list of objects to be slotted

2517879 leLayerAndNot gives different result in IC6.1.8 ISR11 and IC6.1.8 ISR18

2517740 vmtLibImport needs to handle and update part.csv under design management environment properly

2517077 Retain the manual setting +postlpreset=OFF in the GUI when switching between presets

2516787 Point netlisting takes very long time in the DSPF flow

2516371 In hiCreateToggleField, enabledItems is not in sync with enabled attribute

2514702 Delete AGR and Fill option is not displayed in the context menu for merged AGRs

2514129 During concurrent layout editing path segment becomes longer after split if its end segment is outside design partition

2514111 Virtuoso exits unexpectedly: vvSetCurrentWindow after ddtUpdateGraph

2513933 Placement of instances is scattered when virtual hierarchy area boundary is stretched

2513420 If one side of an object is less than or equal to partition area halo, then this side of the object is not split

2513416 Temperature color map at stop time of transient is not displayed

2513400 In a design partition with multiple area boundaries 'Split Object Crossing Partitions' works only for one of them

2513280 LVS fails when the diffstbprobe component is removed from the netlist but not shorted like a voltage source

2513057 The SystemVerilog Netlister creates a netlist with multiple wire declarations resulting in compilation errors

2512989 Double RMB click bindkey for context menu does not work

2512819 Quantus transfer property functionality is missing multi-cell placed device properties

2512655 Netlister is not netlisting VAR expression correctly for some of the points

2512646 Point netlisting takes very long time when the DSPF flow is used

2511466 Digital signals cannot be plotted during an ongoing AMS simulation

2511462 Running an AMS simulation with a single SystemVerilog block gives an *E,WKLNDF error during netlisting

2511239 Bumps alignment check fails after bumps are propagated

2511164 Virtuoso stops responding during Discard Edits when edits are done across multiple tabs

2510116 Virtuoso exits unexpectedly when axlShowHideOutputSetupNamedFilterItems is run

2509633 Error if signal is plotted from HB analysis

2509607 AMS UNL flow gives an error on changing the config view; error points to the Pcell variant

2509111 ADE XL to maestro conversion causing AMS elaboration error for iterated instance varactors

2509013 Virtuoso exits unexpectedly when running EM analysis on a setup using qrcTechFile and emDataFile

2508640 Digital signals cannot be plotted when running simulations from ADE Assembler

2507631 After running an AMS simulation in ADE Assembler, viewing the netlist results in the readTable error

2507458 Virtuoso becomes unresponsive when using the 'Auto adjust area boundary' option with width and utilization

2506956 Error ADE 5019 is reported when trying to disable hysteresis DC analysis in Multi-Test Editor

2506943 Logical trace net bypasses trim layers

2506474 Virtuoso toolbars with extend button do not work properly when using the XFCE desktop

2506416 AMS fault simulation does not work with config DUT

2505856 Virtuoso toolbars with extend button do not work properly when using the XFCE desktop

2503270 Performance diagnosis for library shows 'ldap' server path. Need clarification on what it means

2503215 Layout editing on package level is slow even when extractVerifyInvalidConnections set to nil

2502219 sigType of existing nets and pins change when the sigType of a new net is changed

2502216 A tiny step is generated when a path object split during concurrent layout editing is stretched

2500960 Virtuoso RF: Simulation stops with an incorrect error when mixed sampling type is used for an EMX model

2500494 Results merge with run point selection does not work correctly when clicking the blue run button

2499019 Physical point at which the second event triggers is altered by shapes not related to abutment

2498627 allowedSpacingRanges is not flagging some violations with tapered widths

2497438 Allow the user to set their own EMX settings in UI

2496830 Virtuoso Power Manager does not extract Antennae Diode Related Power Pin for dummy and is always off for devices

2495332 The Compare & Merge flow does not detect deleted rows from a CSV or Microsoft Excel file

2494577 Two area boundaries are generated when pressing Enter key to finish specifying the partition area

2493583 define_signal_attributes do not handle power sniffer circuits having tx gate controls with feedback loop

2493564 Virtuoso Power Manager user-defined macro testing: Switch function and related ground pin change

2492636 DRD check clean is not returning violation markers for maxViaArrayClusterSize with maxFacingEdgeNeighbors

2491689 Display a warning when odd multiple width in a netClass would cause Virtuoso Space-based Router to route offGrid

2491665 Results view shows incorrect values while scrolling

2491480 The Reference Histories form in ADE Assembler does not allow selection of pending simulations

2491054 The 'DC Operating Points' option is greyed out on using Schematic Annotation in Virtuoso

2490528 hiCloseWindow segmentation faults in processOpenCVHasOAException

2488358 Improve via alignment when a minQuadrupleExtension constraint generates an asymmetric via not contained in the overlap

2487607 Running an AMS simulation with a single SystemVerliog block gives an *E,WKLNDF error during netlisting

2485447 Pin net collision after pin name change with new extractor

2483407 axlSetHistoryPrefixInPreRunTrigger allows invalid history names

2483353 Setting the temperature value in the Setting Temperature form clears the temperature specified in the Corners Setup form

2481278 Cannot deselect a trace family by clicking in the background

2481275 Cannot toggle the trace visibility for a trace family by using the context menu

2480612 Search in Data View is slow as it searches all the setup states

2476342 Descend edit for config view does not open schematic view

2467268 Run status shows pending and shows the 'Error while configuring the job' message in job log

2465667 Virtuoso exits unexpectedly due to segmentation fault in hiRaiseWindow

2459654 Signals are not plotted in the Results Browser when running an AMS simulation

2453440 Results view shows incorrect values while scrolling

2450149 In ADE Assembler, results filtering is canceled after interactive toggling of tabs in the Results view

2443148 Export Die will export matching the instance terminal and not the pins on the instance

2442967 Virtuoso stops responding when opening waveforms in Virtuoso Visualization and Analysis XL

2441236 Buttons get removed from the Models column when Reset is clicked after filtering in MTS Options form

2441227 In MTS Options form, clicking Update after adding filters for Library and Cell adds extra rows and extra buttons

2439330 Pin error when generating em_solver extracted view because of schSnapSpacing

2436453 ADE Assembler stops responding for a long time after the column width is auto adjusted if the Results table is bigger than the window size

2435642 Allow canceling of the ADE Assembler Save Setup question that is shown when exiting Virtuoso

2428192 Get 'Ineffective Global Job Policy' pop-up when changing job policy for a maestro view with no tests defined

2427600 Add a placement lock to figGroups

2422944 Calculator gives incorrect results after evaluating the expressions in the Buffer

2420690 hiSetCurrentWinNum segmentation faults

2412237 Properties of ROD multipart path objects not edited as expected when using SKILL

2399151 Virtuoso exits unexpectedly when modifying a multipart path

2399138 Global Signals form does not save changes to existing settings

2295871 All forms are pulled to the foreground when Edit Properties form is invoked in RHEL6 in IC6.1.8 ISR11 and ISR12

2295279 After AMS simulation, plotting a current signal directly from ADE XL shows the WIA-1006 error in CIW

2272466 During fill insertion, add an option to fill neighboring OD shapes belonging to the same row

2255542 Issues in the 'Select Tests are Displayed in Table' list on the Results tab after using the Plot Signal command

2253084 After a post-layout simulation with a DSPF file, unable to plot current data from ADE Assembler, but can plot the same from Results Browser

2249702 Allow signal type check between symbol pin and corresponding schematic pin on same cell

2246134 SKILL function awvPlotExpression gives error for AMS simulations in IC6.1.8; worked fine before

2241695 The 'Select which tests are displayed in table' filter shows all the listed tests as checked even if simulation is not run for all tests

2224397 When the -env ade runSimulation option is used in IC6.1.8, the current expression is different from the one that was added in IC6.1.7

2222105 After running a Spectre APS Monte Carlo simulation with a DSPF cellview, eval error is shown for an IT expression with a node current

2215367 Allow cross-view checker to check for signal type

2214529 Icons in collapsed toolbars are not working

2178982 For external text views, terminal current cannot be saved or plotted due to the '-env ade' argument

2062154 EAD cannot extract a resistance when 'Extraction Mode' is set to 'RC coupled'

2026432 Incorrect well merging because wells are hardcoded to connected 'B' terminals

2014147 Need a cross-view check for sigType property

1994353 Virtuoso stops responding when opening waveforms in Virtuoso Visualization and Analysis XL

1825696 Make sure the design netlist is reused if the same DUT is used for all runs in a run plan

1700431 In ADE Assembler, results filtering is canceled after interactive toggling of tabs in the Results view

1441002 Enhance Cross-View Checker in Layout L to prompt sigType mismatches across views

1147114 Add capability in Cross-View Check to check mismatch of signal type

862348 Check must enforce the same sigType values on pins of the schematic cross views

October 2021

2574047 The mouse cursor for Virtuoso changes for the session after running a simulation with run plan

2573614 Add another parasitic diode flag with the default value as t