Cadence INNOVUS 20.17.00-ISR7 | 49.0 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled INNOVUS 20.17.00-ISR7 is next-generation physical implementation solution that enables system-on-chip (SoC) developers to deliver designs with best-in-class power, performance and area (PPA) while accelerating time to market.

CCMPR02607724 Tool is crashing at signoffOptDesign

CCMPR02606339 pgFill -fix_iso_via need to be mapped in CUI

CCMPR02605437 NRHF PG routing need to improve QoR

CCMPR02604424 fcroute got SEGV with setFlipChipMode -connectPowerCellToBump true option

CCMPR02603596 fcroute SEGV

CCMPR02603526 To reduce trim-related violations seen at route stage

CCMPR02602866 Some hierarchical PG pins are deleting by command delete_dangling_ports

CCMPR02598888 False diffusion core edge length violation

CCMPR02598872 addStripe does not respect spacing to pre-route patch metal

CCMPR02596458 The Operator button in the Find/Select Object form in Innovus 20.x is not working

CCMPR02596175 Trim colors set 0 or 1 even though it is single mask

CCMPR02596009 NanoRoute is trying to access illegal point though it has legal point

CCMPR02595709 UPF file version enhancement to run_clp do generation flow

CCMPR02595355 Innovus makes wrong connections during commit power intent for multibit iso cells (driver->A4, X1-> receiver)

CCMPR02595218 SEGV - place_opt_design

CCMPR02594811 clock_design leaves clock nets in eGR

CCMPR02594657 add_fillers -density flow incorrectly prints the achieved density

CCMPR02594304 NRHF PG routing test for all PG nets got SEGV

CCMPR02594135 editCommitRoute thinks different nets are involved

CCMPR02593223 Convert polygonal verify connectivity open markers to multiple rectangular markers

CCMPR02592700 route_opt (opt_design -post_route) stage getting crashed for CPE block

CCMPR02591283 Top ecoRoute -fix_filler_drc_with_patch_only long runtime issue

CCMPR02589767 set_design_attributes -attribute command error

CCMPR02589541 route_design_crash_at_via_pillar_insertion

CCMPR02589212 PRO timing QOR degradation in 20.16

CCMPR02589116 SEGV occurs when updating RC grid during restoreDesign -mmmcFile

CCMPR02588951 ecoRoute is not fixing EOL DRCs which can be fixed with small patches

CCMPR02588552 route_design errors out with **ERROR: (IMPEXT-4021)

CCMPR02588031 NRHF adding extra shields for vertical layers when applied 2x width on bus groups with interlayer shielding

CCMPR02586956 Timing budget issue (IMPTB-179)

CCMPR02586201 loadFPlan fplan.gz prints DBU in terminal for fences

CCMPR02586162 Query object on GUI prints pointers on terminal.

CCMPR02586013 add_stripes crash at pwsStripeViaGenerateTemplate::encodeTrackOffset

CCMPR02585961 defIn runtime improvement

CCMPR02585478 Enhance pin placement for bottom-up partition pin flow

CCMPR02585063 timeDesign -preplace -hold crash after timeDesign -preplace

CCMPR02584893 NR leaves M11 fuse wires on NDR nets

CCMPR02584767 Signoff flags one missed by NR. Verify caught it as m4 MinStep

CCMPR02583723 Run got stuck during initial detail Routing

CCMPR02583552 NRHF does not work on single net with bus guides

CCMPR02583473 placeSpareModule creating empty spare modules which cannot be deleted

CCMPR02582887 ILM pin to top level disconnected after place_opt_design

CCMPR02582840 POD crashed

CCMPR02581902 High CCOpt CTS runtime

CCMPR02581897 Segmentation Fault during ML training

CCMPR02581409 editPowerVia creates vias with cut spacing/short DRCs

CCMPR02581138 Wrong global element for a PD in the UPF causing domain conflict

CCMPR02581075 M1 shorts created with cell internal Q5 pin while connecting mustjoin CK pins of 8 bit multibit flop

CCMPR02580654 Voltage interpolation of level shifter does not work in block design

CCMPR02579805 saveTestcase/saveDesign command does not update the path of the layermap file in design.mode file

CCMPR02579562 Error message EERROR: (IMPLF-268) needs to be resolved during LEF read

CCMPR02579408 Cannot attachIOBuffer in low power design

CCMPR02578497 Mandatory option: Domain and include_scope are missing in the Innovus wrote out UPF with version

CCMPR02578261 M2 short gap is left

CCMPR02578186 Short/PatchLen violation at core boundary from M2 passiveFill

CCMPR02577962 Hold fixing postCTS with inverters only huge runtime and poor timing results

CCMPR02577606 Clock tree debugger is crashing when we click on skew group in control panel

CCMPR02577394 Wrong coreArea in summaryReport

CCMPR02576956 Detail placer not recognizing via group spacing violations between vias in cell and PG via

CCMPR02576787 routeDesign -passiveFill does not conduct X2 insertion

CCMPR02576780 verify_drc is flagging false M2 EOLK after routeDesign -passiveFill

CCMPR02576769 routeDesign left abnormal X3 trims pattern which causes a lot of violations

CCMPR02576755 routeDesign left hundreds of Off-grid violations

CCMPR02576728 verify_drc and NanoRoute are not detecting trim to trim spacing (positive PRL)

CCMPR02576564 cutRow deletes redundant row

CCMPR02576414 Promoted macro pins seem to be in different direction after pin assignment

CCMPR02576051 Error related to Glitch during PRO

CCMPR02575923 N4_hamoa_top Observing crash during "verifyEndCap" command

CCMPR02575672 Abnormal X3 creation after routeDesign -passiveFill

CCMPR02575288 defIn cannot import net which name is same as instance name from Innovus 20.14

CCMPR02575098 M2 MAXLENGTHWITHCUT viols have room to fix by adding M3 patch, but tool is not patching

CCMPR02575059 VIA3 has same color spacing violations after fastPGRoute

CCMPR02574856 Extra VDD pins are written out from Innovus UPF

CCMPR02573361 place_opt does not honor path adjust (set_path_adjust)

CCMPR02572974 ERROR(IMPOAX-1671) is issued because lef2oa does not generate data.dm

CCMPR02572706 NanoRoute not fixing shorts, when EOL blockage and routing blockage do overlap

CCMPR02572385 Top_only routeDesign -passiveFill long runtime issue

CCMPR02572254 verify_drc: false Trim Obs Shorts at core boundary with X1_VIRTUAL

CCMPR02572178 verify_drc is not detecting TRIM MAXLENGTH

CCMPR02572158 delete_nets on floating net results in AP layer deletion in saved database

CCMPR02571679 False MAXVIASTACK violations in N4 prevent via drop in editPowerVia, addRing

CCMPR02570715 Memory corrupted (MEMPOOL-103) during init_design (syntechFnpPool_INT_0_thread_*)

CCMPR02570603 ecoAddRepeater creates a multi-driver net

CCMPR02569586 CHKPLC-11 showing up for macros NOT in netlist

CCMPR02569540 remove_assigns not honoring dontTouch attribute on the nets

CCMPR02569537 tQRC failure during ROD SO

CCMPR02569530 Innovus crashes during route detail antenna process fix

CCMPR02569295 M1 need to freeze but ecoRoute touch a lot of _SADP_FILLS_RESERVED patch

CCMPR02569279 General routing flow to handle M1 connections even the M1 is frozen

CCMPR02568774 check_design is exiting without stack trace on Innovus

CCMPR02568756 Crash when using set_db log_file

CCMPR02568702 Command add_fillers -density 0.35 hangs for over 12 hours

CCMPR02568595 CCOpt CTS taking high run time to complete

CCMPR02568473 NanoRoute is inserting m6 patch shapes creating a Width_Based_Via_On_NonUniform_Track violations

CCMPR02567588 Observing difference in the PG connection for LS compared to the input UPF is causing an CLP issue

CCMPR02567311 NR SEGV at pthread_join called from export_design

CCMPR02567201 verify_drc missing diff cut spacing DRCs on the PG nets

CCMPR02567156 During ccopt_design -cts: **ERROR: (CCOpt eGR): All passed nets have skipRouting designation and will not be routed

CCMPR02566847 delete_assigns -add_buffer trigger tool SEGV

CCMPR02566727 Poor layer adherence of trunk nets after CCOpt

CCMPR02566412 Arrayed via placements in def being corrupted by write_db

CCMPR02566208 Crash during routeDesign -trackOpt

CCMPR02566199 route blockage changes layers over write_db, read_db

CCMPR02565476 Innovus crashed while doing ccopt_design -cts

CCMPR02565420 Innovus 21.11 place_opt_design crash in OptFanoutOnExcludedClockNets, pre-process of DRV optimizer

CCMPR02564949 add_well_taps crashing with SEGV

CCMPR02564838 Opportunistic full-track without inter-cell routing blockage

CCMPR02564690 addStripe takes long run time

CCMPR02564397 Switched supply net created in lower scope shows up in both lower and top scope

CCMPR02564307 ccopt_design crash

CCMPR02564228 Please set default "false" for droute build 1cpp gap for S2 node

CCMPR02564006 Improve pin access and length near pins

CCMPR02563333 commit_power_intent -verbose crashed

CCMPR02563005 POD hangs when TAT_latch ETF enabled

CCMPR02562766 setPlaceMode -reset -place_detail_exp_target_layers crash issue

CCMPR02562556 sroute is giving a SEGV on Innovus, but runs successfully

CCMPR02561446 routeDesign -trackOpt ends up crashing with stack trace

CCMPR02561230 Innovus crashing in the invs_power_plan stage using command fix_via -short

CCMPR02560471 Placement legalization causing violations when placing mustjoin pins under PG staple

CCMPR02560183 After addFiller there is still a gap

CCMPR02559956 Crashe during routeDesign -toplevel

CCMPR02559805 Same track trim violation can be fixed by merging

CCMPR02559641 fcroute does not route to center of bump

CCMPR02558811 CUI bindkeys get randomly undefined while editing layout

CCMPR02558645 optDesign -postRoute crash during DRV optimization

CCMPR02558390 deriveTimingBudget outputs unnecessary timing arc in budgeted block lib

CCMPR02558382 Please add new violation types for FC layer (max vert stack and horizontal length, spacing, rect only)

CCMPR02558195 Trim shape missing in Innovus even when the patch type and fill type are correct on the shapes abutting trim

CCMPR02557657 Need a solution to tolerate inconsistent pins between lib and LEF (IMPDB-2163, IMPDB-2160)

CCMPR02557509 Innovus crashed at fill stage when using the addStripe command

CCMPR02557234 fcroute causes detour routing around bump

CCMPR02557219 The is_setup attribute is set to true on the delay_corner of the power views

CCMPR02557015 Via Pillar Shorts in M1 due to signal via being marked as special

CCMPR02556705 Command check_place flags false overlapping instances violations

CCMPR02556698 Delay calculation appears to hang during updating delays in ccopt_pro

CCMPR02556578 LEF58_PINCONNECTIONBLOCKAGE interpretation on AP layer is incorrect

CCMPR02556249 trimMetalFillNearNet command trimming wrong layer

CCMPR02556149 get_db returns wrong number of fill shape pointers

CCMPR02555486 addPowerSwitch using the wrong horizontal pitch

CCMPR02555212 #WARNING (NRDB-166) Boundary for CELL_VIEW TopDesign, init is not properly defined

CCMPR02555144 Runtime issue in postroute stage (40 hours) and time_design stage(10 hours)

CCMPR02554376 NanoRoute failed to report Metal_EoL_spacing violations reported by verify

CCMPR02554212 createShield failed but verifyConnectivity passed

CCMPR02553672 Violation Browser should not re-scroll the list of violations when user deletes a violation

CCMPR02553670 Query pop-up box needs to remember where user locates it on the screen

CCMPR02553660 Layer min/max order not consistent between menus

CCMPR02553655 addEndCap high memory foot print and runtime

CCMPR02553297 Huge Jump in TNS during DrvOpt during ccopt_design

CCMPR02553180 route_design moves 99% of reg2reg paths into Default path group

CCMPR02553020 When using CA-routing TLEF, some cells are not placed well under the M2-stripe

CCMPR02552418 Mismatch in shielding ratio values between CTS log and reportShield report

CCMPR02551928 CTS crash

CCMPR02551901 addWellTap caused DRC along boundary of dense LUP layer

CCMPR02551847 Wrong endcap/welltap insertion

CCMPR02551760 Sub-optimal track selection or detoured routes with NR

CCMPR02550942 synthesize_ccopt_flexible_htrees huge runtime of 14Hrs

CCMPR02550813 Insert filler crash

CCMPR02550211 set_promoted_macro_pin is not approximating boundary correctly for round shaped pins

CCMPR02549076 CUI equivalent for fixCellEMViolations

CCMPR02548974 Via Pillar DRCs

CCMPR02548763 Glitch violations are not getting fixed for drv view

CCMPR02548385 Innovus crash during flexible H-tree synthesis

CCMPR02548319 DRC when connecting via pillar to cell

CCMPR02548127 Wide Virtual X3 shows in GUI as 2 X3 shapes

CCMPR02548054 do_extract_model command crashes while generating .libs with -SIAware true

CCMPR02547933 Tool buffers AON net through switched domain and adds regular buffers

CCMPR02547674 Huge runtime seen during TnsOpt pass in postCTS optimization

CCMPR02547291 Unable to place boundary cells due to double height boundary cells

CCMPR02547168 Huge short DRC during exclusive region routing

CCMPR02547128 Generated clock tree does not restore correctly after saveDesign/restoreDesign cycle

CCMPR02546957 No trim at EOL makes trim violation after passiveFill

CCMPR02546744 defOut outputs incorrect DIEAREA

CCMPR02546718 SEGV in POD during TNS opt

CCMPR02545594 Trans fixing is not happening on few nets at with the reason "Could not be fixed because the gain is not enough"

CCMPR02545113 Library links overwritten when using existing OA lib

CCMPR02544268 addStripe causes the tool to crash

CCMPR02544175 Aggressive data to data violation fixing cannot full fix because of CTS constraints

CCMPR02542269 create_rc_corner -postRoute_clkcap TQuantus support

CCMPR02542053 NRHF runtime of max resistance aware routing for multi-fanout net is too long

CCMPR02542030 Multibit flop merging is not happening

CCMPR02541666 check_drc is flagging false m11 trim spacing violations around wide metal line end on NDR track

CCMPR02541509 SEGV at postroute stage while performing report_timing with -SIAware true

CCMPR02541260 Crash with trimMetalFillNearNet with memory pool out of range

CCMPR02540280 assembleDesign with defMerge results on wrong VIA after assemble

CCMPR02540144 Post staple vias causing SMAC(Same Metal Aligned Cuts) from Power Route GenVia

CCMPR02539064 Huge run time hit at two steps/places in global placement

CCMPR02538456 Pre to post route timing correlation

CCMPR02538216 Innovus suspended session has limitation -traversing/tab-autofill does not work

CCMPR02536952 Higher IncrDelayCal runtime during DrvOpt

CCMPR02536584 Ptn pin inconsistency (caused by pinAlignment)

CCMPR02535977 add_io_buffers not inserting buffer on output ports in design with a UPF

CCMPR02535976 MAXVIASTACK rule is not checking correctly

CCMPR02535189 DRC increases when using CA-routing Tech-LEF

CCMPR02534680 Enhance assign_partition_pins command to place signal pins connected to PG nets defined in Verilog

CCMPR02534429 check_design -type opt is taking ~20 hours

CCMPR02534011 Enhance Innovus to have AON buffer insertion be topology aware of the associated secPG stripe

CCMPR02534001 assembleDesign copying MOSAIC prop to instances which are not part of mosaics

CCMPR02533739 Tool crash while running verify_drc

CCMPR02533264 Innovus picks wrong via7 resulting in MinStep and Cut_Enclosure violations

CCMPR02532749 V1 enclosure DRC left when using MUSTUSE syntax in TLEF

CCMPR02530971 sroute fails to correctly route followpins and creates shorts in the presence of a certain power switch cell

CCMPR02530629 dbFTermBox returns wrong location for internal pins

CCMPR02530349 Routing with false autoVia crash issue

CCMPR02530132 editTrim deletes vias after the addStripe command

CCMPR02530123 Timing degraded

CCMPR02530122 NR is making a lot of M1 MAR violation

CCMPR02530077 m4 patch shorts around macro route/trim blockages

CCMPR02530036 FC (diffusion trim) spacing, horiz/vert length, shape rule support is required

CCMPR02529987 opt_design -post_cts added chain of small buffers

CCMPR02527219 Incorrect patch (on 2D routing jogs) causing DRC violations

CCMPR02524544 Enhancement to enforce minimum LVTn/SLVTn density in a specified window/tile size

CCMPR02523811 syn_opt -spatial is taking excessive runtime (53+ hrs) for 3.2M instance design

CCMPR02523523 route_opt run killed

CCMPR02523387 check_macro_place_constraint -net_resistance need to output pin to pin resistance report. Not net based resistance

CCMPR02522071 Support add_partition_feedthrus for master clone design with power domains

CCMPR02522002 route_eco creates shield DRCs on CTS_8400

CCMPR02521940 routeDesign is leaving cut enclosure violations on V3

CCMPR02517837 place_opt_design optimizing out net which leads to a STRATEGY_CTRL_CONN_CONFLICT_ISO fail in CLP

CCMPR02517218 Resizing master partition does not reflect correctly when clone is in MX orientation

CCMPR02517017 Innovus missing TWOWIDTH Spacing Table violation

CCMPR02516287 addFiller does not add global net connections for some VSTACK_POSTFIX cells

CCMPR02515312 create_clock_tree_spec SEGV when set_driving_cell sdc constraint is defined for a cell that has a .lib but not LEF

CCMPR02513224 Tool not fixing metal shorts over M1 pins

CCMPR02511853 saveDesign -no_wait does not release MCPU license tokens licenses forcing extra checkout from the next command

CCMPR02510604 Huge TNS degradation with GlobalClockSkewing just after final PowerReclaim

CCMPR02509758 Huge TAT in POD while doing GigaOpt Optimization in the TNS mode

CCMPR02509196 Partition long runtime on PGCompressed DB

CCMPR02509169 PRO got SEGV at Start delay calculation

CCMPR02509081 Incremental selecting pins does no longer highlight all connected nets

CCMPR02507048 add_stripes adding off track vias

CCMPR02505836 Higher runtime with ecoRoute on already ecoRouted DB

CCMPR02505378 Cut_No_Metal violations in via34

CCMPR02502675 delete_secondary_pg_net requires multiple calls for cells with multiple NWELLS

CCMPR02502598 check_design -type route changes validity of eGR route

CCMPR02502019 verifyConnectivity is showing opens for boundary wires nets

CCMPR02496145 opt vs timer miss match

CCMPR02490795 SEGV in Placement TNS optimization

CCMPR02483153 Routing pattern enhancement to resolve 1P1E rules and to improve timing QoR

CCMPR02482746 addStripe pulls back too far from rBLkg when close to projected line from row-cut edge

CCMPR02482079 DRC Violation Browser to sort DRC categories using lsort -dictionary.

CCMPR02479757 Mustjoin connection shorting with PG stripes

CCMPR02467274 editPowerVia cause cut_spacing violations with -allow_wire_shape_change false

CCMPR02456277 add_filler behavior difference between two versions

CCMPR02455518 Customer requires command to Report PG track utilization per layer

CCMPR02448765 Complex flop not being used with seqCRR at any stage

CCMPR02442606 Buffering is not happening at the place stage due to KEEP_PORT attribute from UPF

CCMPR02431627 Timing and Power degradation in SplitALL flow

CCMPR02431513 Duplicate createSpareModule/placeSpareModule will create corrupted database with duplicate modules

CCMPR02363676 In OA mode, NR should use existing NR_Stack_Via_LEF_DEFAULT_V23_67 instead of creating new ones

CCMPR02291980 Router-friendly swap enhancement for improving utilization push and routability

CCMPR02270410 reportRouteTypeConstraints -svr shows incorrect adherence ratio for via pillar

CCMPR02189837 Detail route force 100% dcut even not required

CCMPR02606339 pgFill -fix_iso_via need to be mapped in CUI

CCMPR02605437 NRHF PG routing need to improve QoR

CCMPR02604424 fcroute got SEGV with setFlipChipMode -connectPowerCellToBump true option

CCMPR02603596 fcroute SEGV

CCMPR02603526 To reduce trim-related violations seen at route stage

CCMPR02602866 Some hierarchical PG pins are deleting by command delete_dangling_ports

CCMPR02598888 False diffusion core edge length violation

CCMPR02598872 addStripe does not respect spacing to pre-route patch metal

CCMPR02596458 The Operator button in the Find/Select Object form in Innovus 20.x is not working

CCMPR02596175 Trim colors set 0 or 1 even though it is single mask

CCMPR02596009 NanoRoute is trying to access illegal point though it has legal point

CCMPR02595709 UPF file version enhancement to run_clp do generation flow

CCMPR02595355 Innovus makes wrong connections during commit power intent for multibit iso cells (driver->A4, X1-> receiver)

CCMPR02595218 SEGV - place_opt_design

CCMPR02594811 clock_design leaves clock nets in eGR

CCMPR02594657 add_fillers -density flow incorrectly prints the achieved density

CCMPR02594304 NRHF PG routing test for all PG nets got SEGV

CCMPR02594135 editCommitRoute thinks different nets are involved

CCMPR02593223 Convert polygonal verify connectivity open markers to multiple rectangular markers

CCMPR02592700 route_opt (opt_design -post_route) stage getting crashed for CPE block

CCMPR02591283 Top ecoRoute -fix_filler_drc_with_patch_only long runtime issue

CCMPR02589767 set_design_attributes -attribute command error

CCMPR02589541 route_design_crash_at_via_pillar_insertion

CCMPR02589212 PRO timing QOR degradation in 20.16

CCMPR02589116 SEGV occurs when updating RC grid during restoreDesign -mmmcFile

CCMPR02588951 ecoRoute is not fixing EOL DRCs which can be fixed with small patches

CCMPR02588552 route_design errors out with **ERROR: (IMPEXT-4021)

CCMPR02588031 NRHF adding extra shields for vertical layers when applied 2x width on bus groups with interlayer shielding

CCMPR02586956 Timing budget issue (IMPTB-179)

CCMPR02586201 loadFPlan fplan.gz prints DBU in terminal for fences

CCMPR02586162 Query object on GUI prints pointers on terminal.

CCMPR02586013 add_stripes crash at pwsStripeViaGenerateTemplate::encodeTrackOffset

CCMPR02585961 defIn runtime improvement

CCMPR02585478 Enhance pin placement for bottom-up partition pin flow

CCMPR02585063 timeDesign -preplace -hold crash after timeDesign -preplace

CCMPR02584893 NR leaves M11 fuse wires on NDR nets

CCMPR02584767 Signoff flags one missed by NR. Verify caught it as m4 MinStep

CCMPR02583723 Run got stuck during initial detail Routing

CCMPR02583552 NRHF does not work on single net with bus guides

CCMPR02583473 placeSpareModule creating empty spare modules which cannot be deleted

CCMPR02582887 ILM pin to top level disconnected after place_opt_design

CCMPR02582840 POD crashed

CCMPR02581902 High CCOpt CTS runtime

CCMPR02581897 Segmentation Fault during ML training

CCMPR02581409 editPowerVia creates vias with cut spacing/short DRCs

CCMPR02581138 Wrong global element for a PD in the UPF causing domain conflict

CCMPR02581075 M1 shorts created with cell internal Q5 pin while connecting mustjoin CK pins of 8 bit multibit flop

CCMPR02580654 Voltage interpolation of level shifter does not work in block design

CCMPR02579805 saveTestcase/saveDesign command does not update the path of the layermap file in design.mode file

CCMPR02579562 Error message EERROR: (IMPLF-268) needs to be resolved during LEF read

CCMPR02579408 Cannot attachIOBuffer in low power design

CCMPR02578497 Mandatory option: Domain and include_scope are missing in the Innovus wrote out UPF with version

CCMPR02578261 M2 short gap is left

CCMPR02578186 Short/PatchLen violation at core boundary from M2 passiveFill

CCMPR02577962 Hold fixing postCTS with inverters only huge runtime and poor timing results

CCMPR02577606 Clock tree debugger is crashing when we click on skew group in control panel

CCMPR02577394 Wrong coreArea in summaryReport

CCMPR02576956 Detail placer not recognizing via group spacing violations between vias in cell and PG via

CCMPR02576787 routeDesign -passiveFill does not conduct X2 insertion

CCMPR02576780 verify_drc is flagging false M2 EOLK after routeDesign -passiveFill

CCMPR02576769 routeDesign left abnormal X3 trims pattern which causes a lot of violations

CCMPR02576755 routeDesign left hundreds of Off-grid violations

CCMPR02576728 verify_drc and NanoRoute are not detecting trim to trim spacing (positive PRL)

CCMPR02576564 cutRow deletes redundant row

CCMPR02576414 Promoted macro pins seem to be in different direction after pin assignment

CCMPR02576051 Error related to Glitch during PRO

CCMPR02575923 N4_hamoa_top Observing crash during "verifyEndCap" command

CCMPR02575672 Abnormal X3 creation after routeDesign -passiveFill

CCMPR02575288 defIn cannot import net which name is same as instance name from Innovus 20.14

CCMPR02575098 M2 MAXLENGTHWITHCUT viols have room to fix by adding M3 patch, but tool is not patching

CCMPR02575059 VIA3 has same color spacing violations after fastPGRoute

CCMPR02574856 Extra VDD pins are written out from Innovus UPF

CCMPR02573361 place_opt does not honor path adjust (set_path_adjust)

CCMPR02572974 ERROR(IMPOAX-1671) is issued because lef2oa does not generate data.dm

CCMPR02572706 NanoRoute not fixing shorts, when EOL blockage and routing blockage do overlap

CCMPR02572385 Top_only routeDesign -passiveFill long runtime issue

CCMPR02572254 verify_drc: false Trim Obs Shorts at core boundary with X1_VIRTUAL

CCMPR02572178 verify_drc is not detecting TRIM MAXLENGTH

CCMPR02572158 delete_nets on floating net results in AP layer deletion in saved database

CCMPR02571679 False MAXVIASTACK violations in N4 prevent via drop in editPowerVia, addRing

CCMPR02570715 Memory corrupted (MEMPOOL-103) during init_design (syntechFnpPool_INT_0_thread_*)

CCMPR02570603 ecoAddRepeater creates a multi-driver net

CCMPR02569586 CHKPLC-11 showing up for macros NOT in netlist

CCMPR02569540 remove_assigns not honoring dontTouch attribute on the nets

CCMPR02569537 tQRC failure during ROD SO

CCMPR02569530 Innovus crashes during route detail antenna process fix

CCMPR02569295 M1 need to freeze but ecoRoute touch a lot of _SADP_FILLS_RESERVED patch

CCMPR02569279 General routing flow to handle M1 connections even the M1 is frozen

CCMPR02568774 check_design is exiting without stack trace on Innovus

CCMPR02568756 Crash when using set_db log_file

CCMPR02568702 Command add_fillers -density 0.35 hangs for over 12 hours

CCMPR02568595 CCOpt CTS taking high run time to complete

CCMPR02568473 NanoRoute is inserting m6 patch shapes creating a Width_Based_Via_On_NonUniform_Track violations

CCMPR02567588 Observing difference in the PG connection for LS compared to the input UPF is causing an CLP issue

CCMPR02567311 NR SEGV at pthread_join called from export_design

CCMPR02567201 verify_drc missing diff cut spacing DRCs on the PG nets

CCMPR02567156 During ccopt_design -cts: **ERROR: (CCOpt eGR): All passed nets have skipRouting designation and will not be routed

CCMPR02566847 delete_assigns -add_buffer trigger tool SEGV

CCMPR02566727 Poor layer adherence of trunk nets after CCOpt

CCMPR02566412 Arrayed via placements in def being corrupted by write_db

CCMPR02566208 Crash during routeDesign -trackOpt

CCMPR02566199 route blockage changes layers over write_db, read_db

CCMPR02565476 Innovus crashed while doing ccopt_design -cts

CCMPR02565420 Innovus 21.11 place_opt_design crash in OptFanoutOnExcludedClockNets, pre-process of DRV optimizer

CCMPR02564949 add_well_taps crashing with SEGV

CCMPR02564838 Opportunistic full-track without inter-cell routing blockage

CCMPR02564690 addStripe takes long run time

CCMPR02564397 Switched supply net created in lower scope shows up in both lower and top scope

CCMPR02564307 ccopt_design crash

CCMPR02564228 Please set default "false" for droute build 1cpp gap for S2 node

CCMPR02564006 Improve pin access and length near pins

CCMPR02563333 commit_power_intent -verbose crashed

CCMPR02563005 POD hangs when TAT_latch ETF enabled

CCMPR02562766 setPlaceMode -reset -place_detail_exp_target_layers crash issue

CCMPR02562556 sroute is giving a SEGV on Innovus, but runs successfully

CCMPR02561446 routeDesign -trackOpt ends up crashing with stack trace

CCMPR02561230 Innovus crashing in the invs_power_plan stage using command fix_via -short

CCMPR02560471 Placement legalization causing violations when placing mustjoin pins under PG staple

CCMPR02560183 After addFiller there is still a gap

CCMPR02559956 Crashe during routeDesign -toplevel

CCMPR02559805 Same track trim violation can be fixed by merging

CCMPR02559641 fcroute does not route to center of bump

CCMPR02558811 CUI bindkeys get randomly undefined while editing layout

CCMPR02558645 optDesign -postRoute crash during DRV optimization

CCMPR02558390 deriveTimingBudget outputs unnecessary timing arc in budgeted block lib

CCMPR02558382 Please add new violation types for FC layer (max vert stack and horizontal length, spacing, rect only)

CCMPR02558195 Trim shape missing in Innovus even when the patch type and fill type are correct on the shapes abutting trim

CCMPR02557657 Need a solution to tolerate inconsistent pins between lib and LEF (IMPDB-2163, IMPDB-2160)

CCMPR02557509 Innovus crashed at fill stage when using the addStripe command

CCMPR02557234 fcroute causes detour routing around bump

CCMPR02557219 The is_setup attribute is set to true on the delay_corner of the power views

CCMPR02557015 Via Pillar Shorts in M1 due to signal via being marked as special

CCMPR02556705 Command check_place flags false overlapping instances violations

CCMPR02556698 Delay calculation appears to hang during updating delays in ccopt_pro

CCMPR02556578 LEF58_PINCONNECTIONBLOCKAGE interpretation on AP layer is incorrect

CCMPR02556249 trimMetalFillNearNet command trimming wrong layer

CCMPR02556149 get_db returns wrong number of fill shape pointers

CCMPR02555486 addPowerSwitch using the wrong horizontal pitch

CCMPR02555212 #WARNING (NRDB-166) Boundary for CELL_VIEW TopDesign, init is not properly defined

CCMPR02555144 Runtime issue in postroute stage (40 hours) and time_design stage(10 hours)

CCMPR02554376 NanoRoute failed to report Metal_EoL_spacing violations reported by verify

CCMPR02554212 createShield failed but verifyConnectivity passed

CCMPR02553672 Violation Browser should not re-scroll the list of violations when user deletes a violation

CCMPR02553670 Query pop-up box needs to remember where user locates it on the screen

CCMPR02553660 Layer min/max order not consistent between menus

CCMPR02553655 addEndCap high memory foot print and runtime

CCMPR02553297 Huge Jump in TNS during DrvOpt during ccopt_design

CCMPR02553180 route_design moves 99% of reg2reg paths into Default path group

CCMPR02553020 When using CA-routing TLEF, some cells are not placed well under the M2-stripe

CCMPR02552418 Mismatch in shielding ratio values between CTS log and reportShield report

CCMPR02551928 CTS crash

CCMPR02551901 addWellTap caused DRC along boundary of dense LUP layer

CCMPR02551847 Wrong endcap/welltap insertion

CCMPR02551760 Sub-optimal track selection or detoured routes with NR

CCMPR02550942 synthesize_ccopt_flexible_htrees huge runtime of 14Hrs

CCMPR02550813 Insert filler crash

CCMPR02550211 set_promoted_macro_pin is not approximating boundary correctly for round shaped pins

CCMPR02549076 CUI equivalent for fixCellEMViolations

CCMPR02548974 Via Pillar DRCs

CCMPR02548763 Glitch violations are not getting fixed for drv view

CCMPR02548385 Innovus crash during flexible H-tree synthesis

CCMPR02548319 DRC when connecting via pillar to cell

CCMPR02548127 Wide Virtual X3 shows in GUI as 2 X3 shapes

CCMPR02548054 do_extract_model command crashes while generating .libs with -SIAware true

CCMPR02547933 Tool buffers AON net through switched domain and adds regular buffers

CCMPR02547674 Huge runtime seen during TnsOpt pass in postCTS optimization

CCMPR02547291 Unable to place boundary cells due to double height boundary cells

CCMPR02547168 Huge short DRC during exclusive region routing

CCMPR02547128 Generated clock tree does not restore correctly after saveDesign/restoreDesign cycle

CCMPR02546957 No trim at EOL makes trim violation after passiveFill

CCMPR02546744 defOut outputs incorrect DIEAREA

CCMPR02546718 SEGV in POD during TNS opt

CCMPR02545594 Trans fixing is not happening on few nets at with the reason "Could not be fixed because the gain is not enough"

CCMPR02545113 Library links overwritten when using existing OA lib

CCMPR02544268 addStripe causes the tool to crash

CCMPR02544175 Aggressive data to data violation fixing cannot full fix because of CTS constraints

CCMPR02542269 create_rc_corner -postRoute_clkcap TQuantus support

CCMPR02542053 NRHF runtime of max resistance aware routing for multi-fanout net is too long

CCMPR02542030 Multibit flop merging is not happening

CCMPR02541666 check_drc is flagging false m11 trim spacing violations around wide metal line end on NDR track

CCMPR02541509 SEGV at postroute stage while performing report_timing with -SIAware true

CCMPR02541260 Crash with trimMetalFillNearNet with memory pool out of range

CCMPR02540280 assembleDesign with defMerge results on wrong VIA after assemble

CCMPR02540144 Post staple vias causing SMAC(Same Metal Aligned Cuts) from Power Route GenVia

CCMPR02539064 Huge run time hit at two steps/places in global placement

CCMPR02538456 Pre to post route timing correlation

CCMPR02538216 Innovus suspended session has limitation -traversing/tab-autofill does not work

CCMPR02536952 Higher IncrDelayCal runtime during DrvOpt

CCMPR02536584 Ptn pin inconsistency (caused by pinAlignment)

CCMPR02535977 add_io_buffers not inserting buffer on output ports in design with a UPF

CCMPR02535976 MAXVIASTACK rule is not checking correctly

CCMPR02535189 DRC increases when using CA-routing Tech-LEF

CCMPR02534680 Enhance assign_partition_pins command to place signal pins connected to PG nets defined in Verilog

CCMPR02534429 check_design -type opt is taking ~20 hours

CCMPR02534011 Enhance Innovus to have AON buffer insertion be topology aware of the associated secPG stripe

CCMPR02534001 assembleDesign copying MOSAIC prop to instances which are not part of mosaics

CCMPR02533739 Tool crash while running verify_drc

CCMPR02533264 Innovus picks wrong via7 resulting in MinStep and Cut_Enclosure violations

CCMPR02532749 V1 enclosure DRC left when using MUSTUSE syntax in TLEF

CCMPR02530971 sroute fails to correctly route followpins and creates shorts in the presence of a certain power switch cell

CCMPR02530629 dbFTermBox returns wrong location for internal pins

CCMPR02530349 Routing with false autoVia crash issue

CCMPR02530132 editTrim deletes vias after the addStripe command

CCMPR02530123 Timing degraded

CCMPR02530122 NR is making a lot of M1 MAR violation

CCMPR02530077 m4 patch shorts around macro route/trim blockages

CCMPR02530036 FC (diffusion trim) spacing, horiz/vert length, shape rule support is required

CCMPR02529987 opt_design -post_cts added chain of small buffers

CCMPR02527219 Incorrect patch (on 2D routing jogs) causing DRC violations

CCMPR02524544 Enhancement to enforce minimum LVTn/SLVTn density in a specified window/tile size

CCMPR02523811 syn_opt -spatial is taking excessive runtime (53+ hrs) for 3.2M instance design

CCMPR02523523 route_opt run killed

CCMPR02523387 check_macro_place_constraint -net_resistance need to output pin to pin resistance report. Not net based resistance

CCMPR02522071 Support add_partition_feedthrus for master clone design with power domains

CCMPR02522002 route_eco creates shield DRCs on CTS_8400

CCMPR02521940 routeDesign is leaving cut enclosure violations on V3

CCMPR02517837 place_opt_design optimizing out net which leads to a STRATEGY_CTRL_CONN_CONFLICT_ISO fail in CLP

CCMPR02517218 Resizing master partition does not reflect correctly when clone is in MX orientation

CCMPR02517017 Innovus missing TWOWIDTH Spacing Table violation

CCMPR02516287 addFiller does not add global net connections for some VSTACK_POSTFIX cells

CCMPR02515312 create_clock_tree_spec SEGV when set_driving_cell sdc constraint is defined for a cell that has a .lib but not LEF

CCMPR02513224 Tool not fixing metal shorts over M1 pins

CCMPR02511853 saveDesign -no_wait does not release MCPU license tokens licenses forcing extra checkout from the next command

CCMPR02510604 Huge TNS degradation with GlobalClockSkewing just after final PowerReclaim

CCMPR02509758 Huge TAT in POD while doing GigaOpt Optimization in the TNS mode

CCMPR02509196 Partition long runtime on PGCompressed DB

CCMPR02509169 PRO got SEGV at Start delay calculation

CCMPR02509081 Incremental selecting pins does no longer highlight all connected nets

CCMPR02507048 add_stripes adding off track vias

CCMPR02505836 Higher runtime with ecoRoute on already ecoRouted DB

CCMPR02505378 Cut_No_Metal violations in via34

CCMPR02502675 delete_secondary_pg_net requires multiple calls for cells with multiple NWELLS

CCMPR02502598 check_design -type route changes validity of eGR route

CCMPR02502019 verifyConnectivity is showing opens for boundary wires nets

CCMPR02496145 opt vs timer miss match

CCMPR02490795 SEGV in Placement TNS optimization

CCMPR02483153 Routing pattern enhancement to resolve 1P1E rules and to improve timing QoR

CCMPR02482746 addStripe pulls back too far from rBLkg when close to projected line from row-cut edge

CCMPR02482079 DRC Violation Browser to sort DRC categories using lsort -dictionary.

CCMPR02479757 Mustjoin connection shorting with PG stripes

CCMPR02467274 editPowerVia cause cut_spacing violations with -allow_wire_shape_change false

CCMPR02456277 add_filler behavior difference between two versions

CCMPR02455518 Customer requires command to Report PG track utilization per layer

CCMPR02448765 Complex flop not being used with seqCRR at any stage

CCMPR02442606 Buffering is not happening at the place stage due to KEEP_PORT attribute from UPF

CCMPR02431627 Timing and Power degradation in SplitALL flow

CCMPR02431513 Duplicate createSpareModule/placeSpareModule will create corrupted database with duplicate modules

CCMPR02363676 In OA mode, NR should use existing NR_Stack_Via_LEF_DEFAULT_V23_67 instead of creating new ones

CCMPR02291980 Router-friendly swap enhancement for improving utilization push and routability

CCMPR02270410 reportRouteTypeConstraints -svr shows incorrect adherence ratio for via pillar

CCMPR02189837 Detail route force 100% dcut even not required

The Innovus Implementation System is a massively parallel physical implementation system that enables engineers to deliver high-quality designs with competitive power, performance and area (PPA) targets while accelerating time to market. It is a part of the Cadence digital design platform that supports the company’s overall System Design Enablement strategy, which enables system and semiconductor companies to create complete, differentiated end products more efficiently.

Place and Route in Cadence Innovus

Complete flow of innovus tool has been demonstrated in this video. Both command line and GUI mode have been covered in the same video. Important input files for this flow has also been discussed and how to create them has been explained.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For nine years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work For.

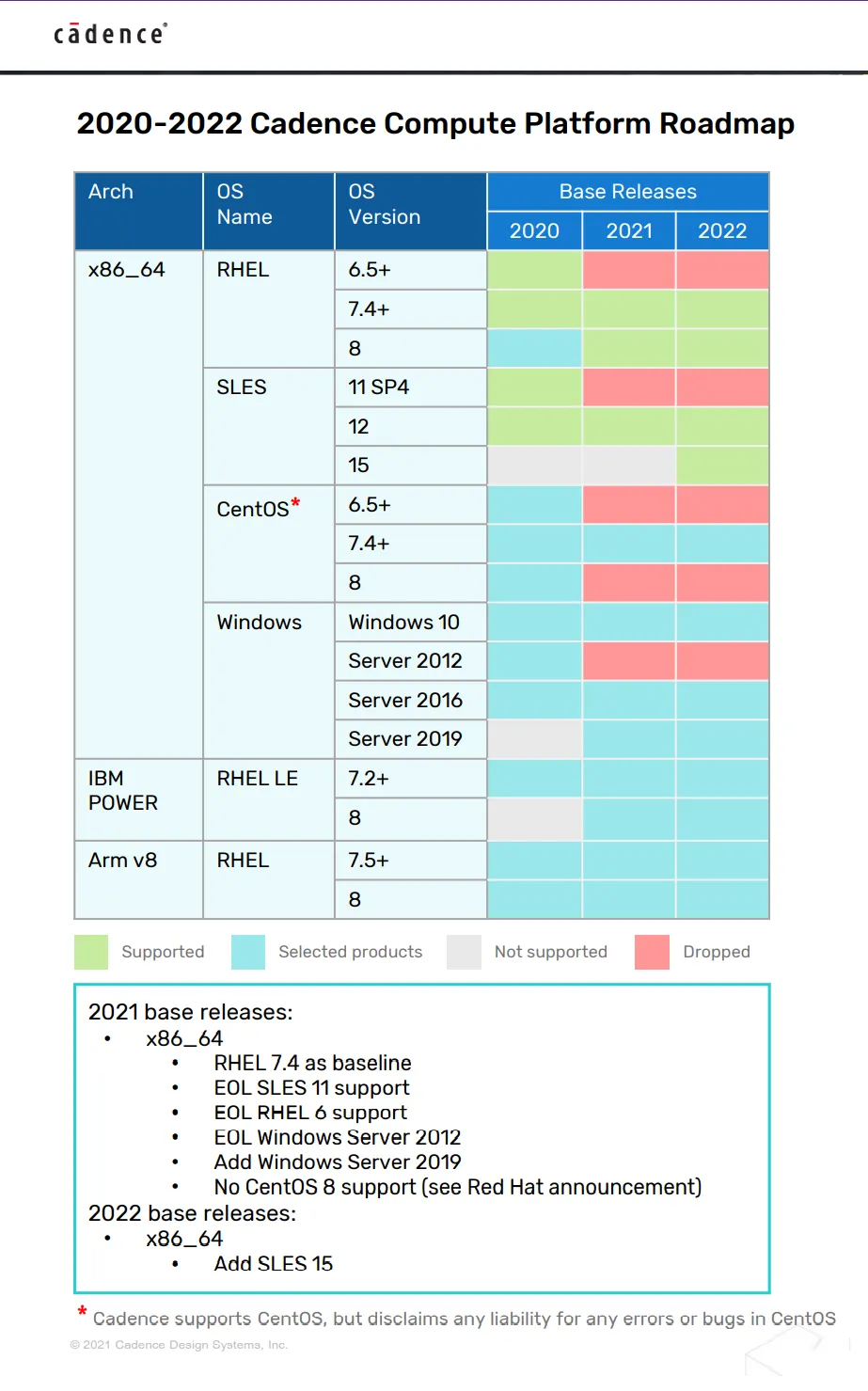

Owner: Cadence Design Systems, Inc.

Product Name: INNOVUS Implementation System

Version: 20.17.00-ISR7 *

Supported Platform: lnx86

Website Home Page : ww.cadence.com

Languages Supported: english

System Requirements: Linux **

Size: 49.0 Gb

Base_INNOVUS20.10.000_lnx86

Hotfix_INNOVUS20.11.000-ISR1_lnx86

Hotfix_INNOVUS20.12.000-ISR2_lnx86

Hotfix_INNOVUS20.13.000-ISR3_lnx86

Hotfix_INNOVUS20.14.000-ISR4_lnx86

Hotfix_INNOVUS20.15.000-ISR5_lnx86

Hotfix_INNOVUS20.16.000-ISR6_lnx86

Hotfix_INNOVUS20.17.000-ISR7_lnx86

Hotfix_INNOVUS20.11.000-ISR1_lnx86

Hotfix_INNOVUS20.12.000-ISR2_lnx86

Hotfix_INNOVUS20.13.000-ISR3_lnx86

Hotfix_INNOVUS20.14.000-ISR4_lnx86

Hotfix_INNOVUS20.15.000-ISR5_lnx86

Hotfix_INNOVUS20.16.000-ISR6_lnx86

Hotfix_INNOVUS20.17.000-ISR7_lnx86

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please